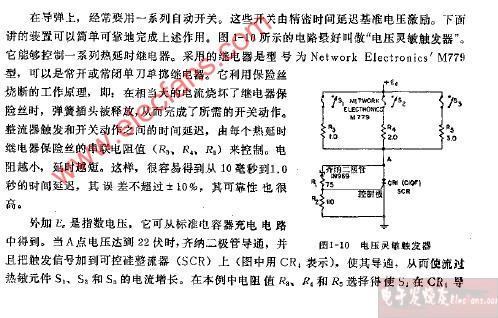

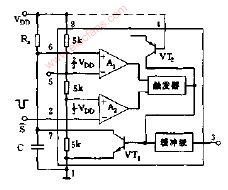

觸發(fā)器的輸入電路圖

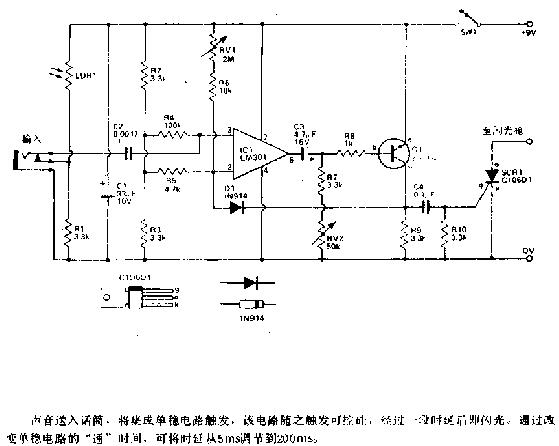

- 觸發(fā)器(59899)

相關(guān)推薦

rs觸發(fā)器為什么不能都為1

rs觸發(fā)器為什么不能都為1? RS觸發(fā)器屬于數(shù)字電路中的一種重要的鎖存器。它由兩個(gè)輸入端和兩個(gè)輸出端組成。理論上,輸入信號(hào)可以為任意值,包括1或0。但是,在實(shí)際應(yīng)用中,不能讓RS觸發(fā)器的兩個(gè)輸入信號(hào)

2023-09-17 14:47:12 341

341

341

341rs觸發(fā)器和d觸發(fā)器的區(qū)別 鐘控rs觸發(fā)器的作用是什么

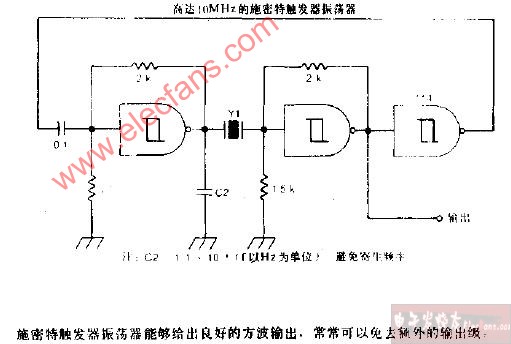

由于RS觸發(fā)器實(shí)現(xiàn)方式的不同,對(duì)輸入信號(hào)抖動(dòng)(即短時(shí)間內(nèi)多次變化)的響應(yīng)也不同。原始的電路設(shè)計(jì)可能導(dǎo)致RS觸發(fā)器對(duì)輸入信號(hào)的抖動(dòng)比較敏感。

2023-09-07 15:47:45 683

683

683

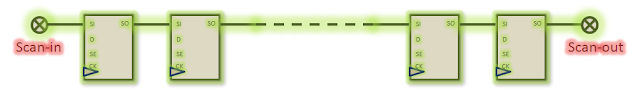

683普通觸發(fā)器如何轉(zhuǎn)換為掃描觸發(fā)器

什么是掃描鏈: 掃描鏈?zhǔn)腔趻呙璧脑O(shè)計(jì)中的元素,用于移進(jìn)和移出測(cè)試數(shù)據(jù)。掃描鏈由連接在鏈中的多個(gè)觸發(fā)器構(gòu)成,其中一個(gè)觸發(fā)器的輸出連接到另一個(gè)觸發(fā)器。第一觸發(fā)器的輸入連接到芯片的輸入引腳(稱為掃描入

2023-08-25 17:01:16 180

180

180

180

觸發(fā)器的輸出狀態(tài)由什么決定

觸發(fā)器的輸出狀態(tài)由什么決定? 觸發(fā)器是一種數(shù)字電路元件,用于存儲(chǔ)和轉(zhuǎn)換電信號(hào)。它通常由幾個(gè)門電路構(gòu)成,并能夠在符合特定條件時(shí)改變輸出狀態(tài)。觸發(fā)器的輸出狀態(tài)是由輸入信號(hào)和內(nèi)部反饋電路共同決定的。在本篇

2023-08-24 15:50:23 276

276

276

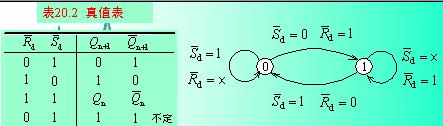

276數(shù)字電路中的RS觸發(fā)器詳解

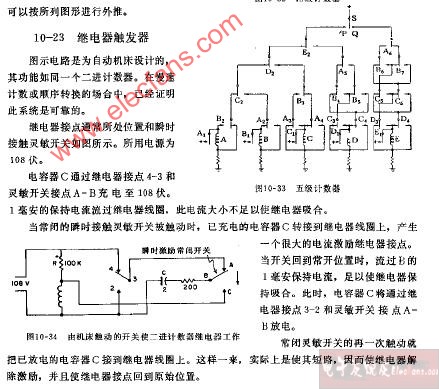

其中R、S分別是英文復(fù)位Reset和置位Set的縮寫,作為最簡(jiǎn)單的一種觸發(fā)器,是構(gòu)成各種復(fù)雜觸發(fā)器的基礎(chǔ)。RS觸發(fā)器的邏輯電路圖如下圖所示。

2023-02-08 09:19:45 2572

2572

2572

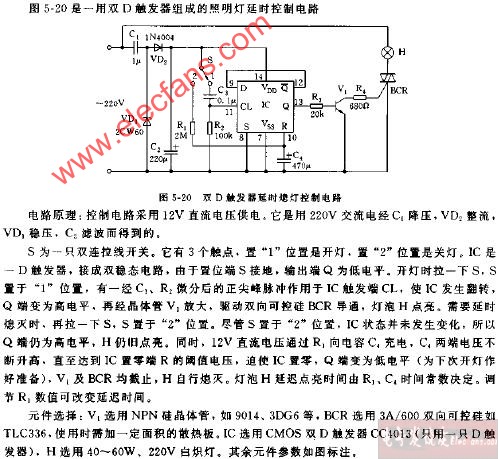

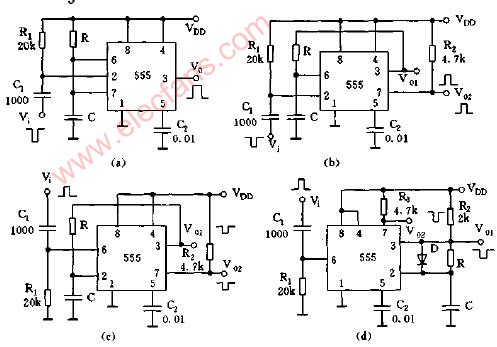

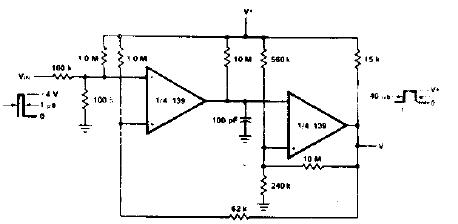

2572D觸發(fā)器不同應(yīng)用下的電路圖

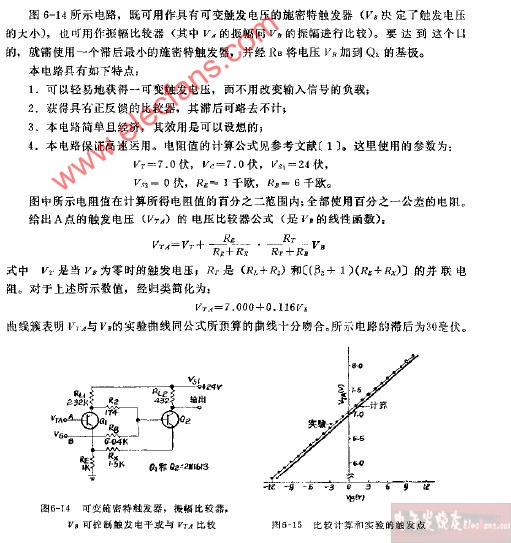

觸發(fā)器也是單個(gè)寄存器,當(dāng)一個(gè)寄存器設(shè)計(jì)有多個(gè)觸發(fā)器時(shí),可以存儲(chǔ)一位,可以容納更多位數(shù)據(jù)。最后,移位寄存器是一種用于存儲(chǔ)或傳輸數(shù)據(jù)的邏輯電路。

2023-01-06 14:22:09 554

554

554

554D觸發(fā)器不同應(yīng)用下的電路圖詳解

D 觸發(fā)器或數(shù)據(jù)觸發(fā)器是一種觸發(fā)器,它只有一個(gè)數(shù)據(jù)輸入“D”和一個(gè)時(shí)鐘脈沖輸入, 這種觸發(fā)器也稱為延遲觸發(fā)器,經(jīng)常用于許多時(shí)序電路,如寄存器、計(jì)數(shù)器等。下面一起來了解一下D觸發(fā)器不同應(yīng)用下的電路圖。

2023-01-06 14:19:46 1874

1874

1874

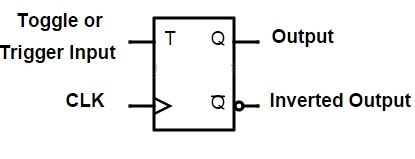

1874T觸發(fā)器的設(shè)計(jì)

T觸發(fā)器,英文名為“Toggle Flip – flop”。為了避免SR觸發(fā)器出現(xiàn)中間狀態(tài)(也稱為禁止?fàn)顟B(tài)),一般只給觸發(fā)器提供一個(gè)輸入,這稱為觸發(fā)輸入或切換輸入(T)。然后,觸發(fā)器用作切換開關(guān)。切換意味著“將下一狀態(tài)輸出更改為當(dāng)前狀態(tài)輸出的補(bǔ)充”。

2022-10-31 16:21:02 5170

5170

5170

5170

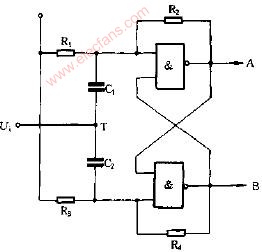

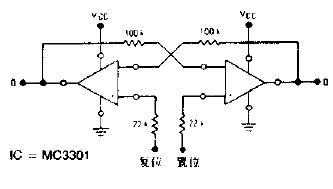

rs觸發(fā)器電路圖與rs觸發(fā)器內(nèi)部電路圖

rs觸發(fā)器電路圖與rs觸發(fā)器內(nèi)部電路圖 rs觸發(fā)器電路圖 主從RS觸發(fā)器電路圖: 主從觸發(fā)器由兩級(jí)觸發(fā)器構(gòu)成,其中一級(jí)接收輸入信號(hào),其狀態(tài)直接由輸入信號(hào)決定,稱為主觸發(fā)器,還有一級(jí)的輸入與主觸發(fā)器

2022-10-19 19:16:03 16964

16964

16964

16964

RS觸發(fā)器是什么?解讀rs觸發(fā)器的作用和數(shù)字電路中的rs觸發(fā)器的作用

什么是RS觸發(fā)器 其中R、S分別是英文復(fù)位 Reset 和置位 Set 的縮寫,作為最簡(jiǎn)單的一種觸發(fā)器,是構(gòu)成各種復(fù)雜觸發(fā)器的基礎(chǔ)。RS觸發(fā)器的邏輯電路圖如下圖所示。 RS觸發(fā)器可以用與非門實(shí)現(xiàn)或者

2022-10-19 17:49:59 5720

5720

5720

5720

三態(tài)RS觸發(fā)器的Multisim仿真實(shí)例電路圖免費(fèi)下載

本文檔的主要內(nèi)容詳細(xì)介紹的是三態(tài)RS觸發(fā)器的Multisim仿真實(shí)例電路圖免費(fèi)下載。

2020-09-03 18:30:06 29

29

29

29RS觸發(fā)器的研究的仿真電路圖免費(fèi)下載

本文檔的主要內(nèi)容詳細(xì)介紹的是RS觸發(fā)器的研究的仿真電路圖免費(fèi)下載。

2020-07-17 16:43:53 27

27

27

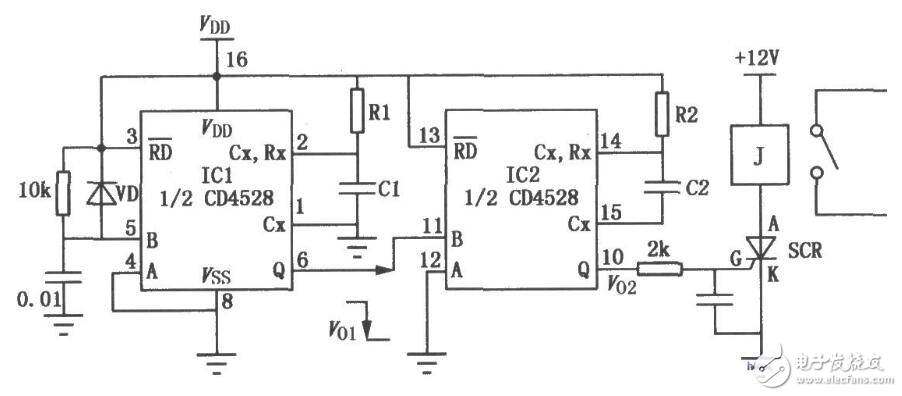

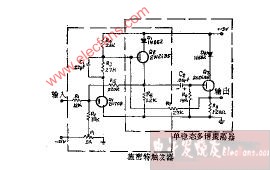

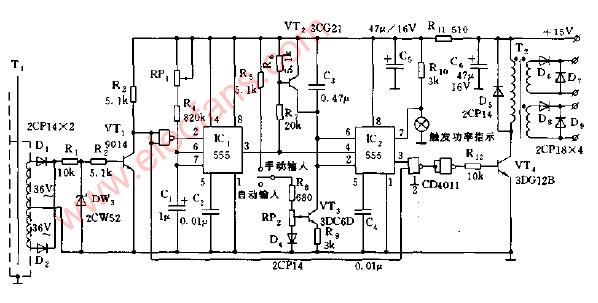

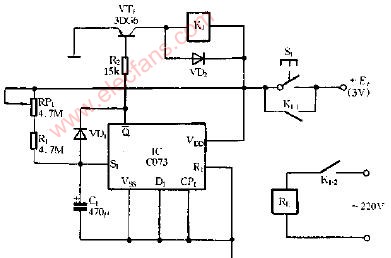

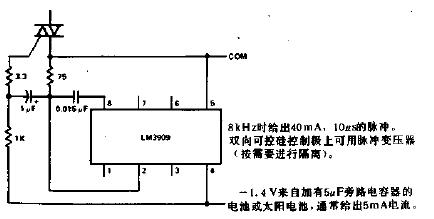

27單穩(wěn)態(tài)觸發(fā)器延遲電路

單穩(wěn)態(tài)觸發(fā)器CD4528組成的延時(shí)電路圖如下:?jiǎn)畏€(wěn)態(tài)觸發(fā)器電路處于穩(wěn)態(tài)時(shí),由于反相器D2輸入端經(jīng)R接+VDD,其輸出端為0,耦合至D1輸入端使D1輸出端為1,電容C兩端電位相等,無壓降。

2019-08-05 15:19:31 17327

17327

17327

17327

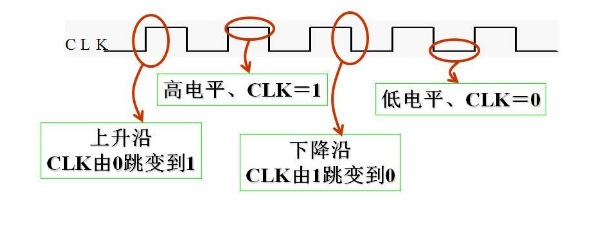

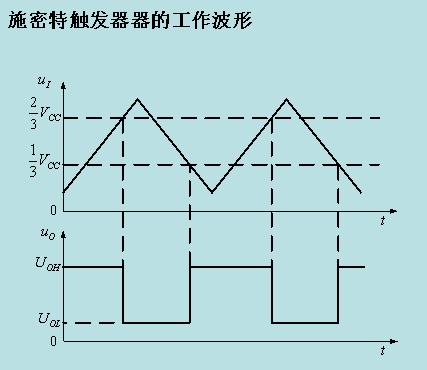

邊沿觸發(fā)器波形圖

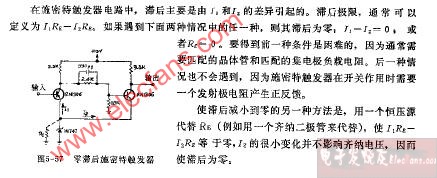

主從觸發(fā)器可以有效克服鐘控觸發(fā)器的空翻現(xiàn)象,但主從觸發(fā)器還存在一次翻轉(zhuǎn)現(xiàn)象,降低了抗干擾能力。邊沿觸發(fā)器:只有在CP的上升沿(前沿)或下降沿(后沿)時(shí)刻才對(duì)輸入信號(hào)響應(yīng)(不管CP=1的時(shí)間有多長(zhǎng))。在CP=0、CP=1期間,輸入信號(hào)變化不會(huì)引起觸發(fā)器狀態(tài)的變化。

2018-01-31 10:38:34 22623

22623

22623

22623

什么是邊沿觸發(fā)器_邊沿D觸發(fā)器介紹

邊沿觸發(fā)器,指的是接收時(shí)鐘脈沖CP 的某一約定跳變(正跳變或負(fù)跳變)來到時(shí)的輸入數(shù)據(jù)。在CP=l 及CP=0 期間以及CP非約定跳變到來時(shí),觸發(fā)器不接收數(shù)據(jù)的觸發(fā)器。具有下列特點(diǎn)的觸發(fā)器稱為邊沿觸發(fā)方式觸發(fā)器,簡(jiǎn)稱邊沿觸發(fā)器。

2018-01-31 09:02:33 68254

68254

68254

68254

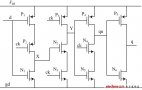

TSPC電路構(gòu)成的觸發(fā)器電路

TSPC電路構(gòu)成的觸發(fā)器電路由四級(jí)反相器構(gòu)成, 上升沿觸發(fā), 當(dāng)CK 為低電平, 輸入反相器在節(jié)點(diǎn)X 上采樣反向d 輸入.

2011-11-25 15:21:27 29856

29856

29856

29856

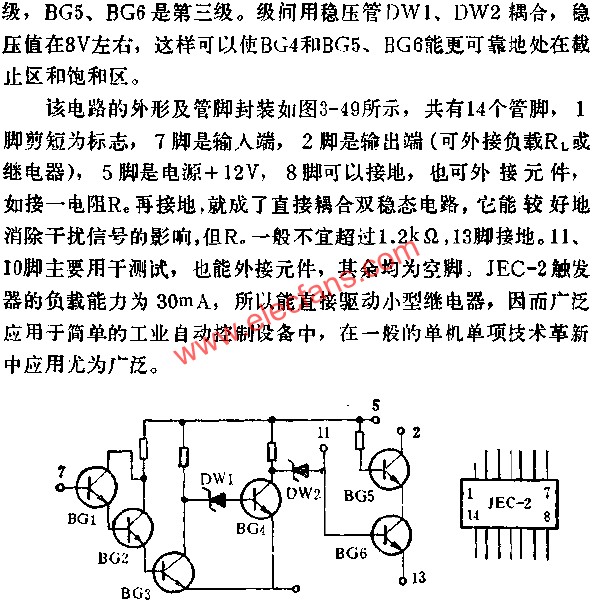

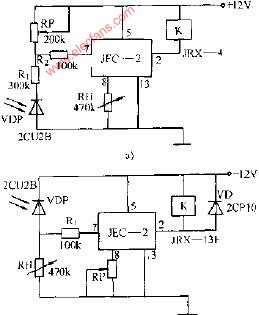

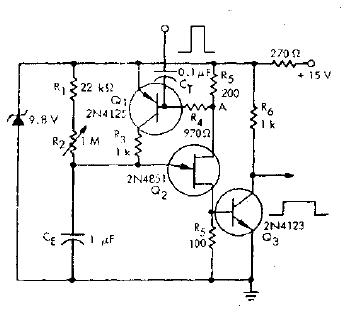

JEC-2觸發(fā)器電路圖

JEC-2射極耦合觸發(fā)器,又稱多功能觸發(fā)器,它雖然叫觸發(fā)器,實(shí)際上是一個(gè)三極反相器的聯(lián)級(jí)電路,如圖所示。

2010-09-25 22:20:30 2073

2073

2073

2073

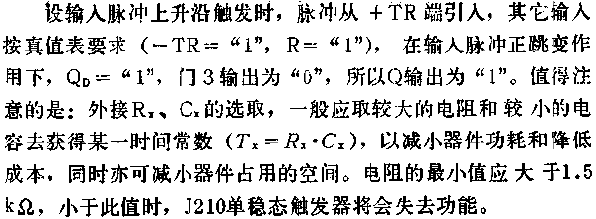

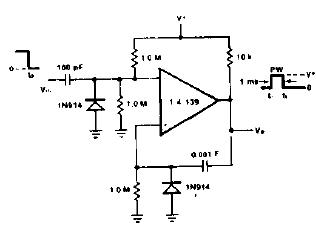

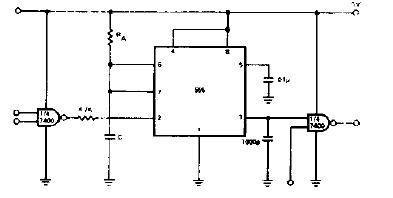

J210觸發(fā)器電路圖

J210集成電路有兩個(gè)相同的單穩(wěn)態(tài)觸發(fā)器,它由D觸發(fā)器、門電路以及由PMQS和NMOS管構(gòu)成的三態(tài)電路組成。圖中

2010-09-24 01:18:20 776

776

776

776

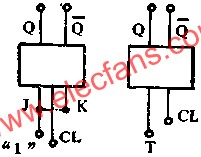

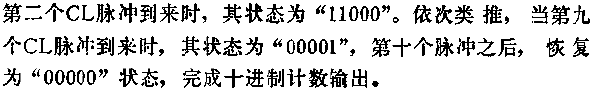

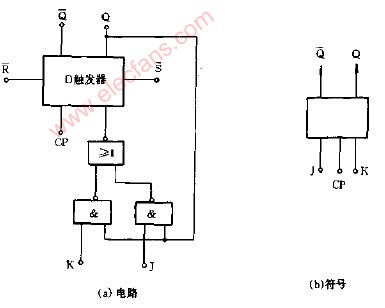

J-K觸發(fā)器組成T觸發(fā)器電路圖

圖中所示是J-K觸發(fā)器組成T觸發(fā)器的電路和邏輯符號(hào)。將J端和K端連接,作為T端,它的功能是當(dāng)T=“1”,即J,K

2010-09-24 00:26:06 6756

6756

6756

6756

J-K觸發(fā)器組成D觸發(fā)器電路圖

圖中所示是用J-K觸發(fā)器組成的D觸發(fā)器電路。

從J-K觸發(fā)器的邏輯圖已知在D觸發(fā)器端增

2010-09-24 00:21:27 5729

5729

5729

5729

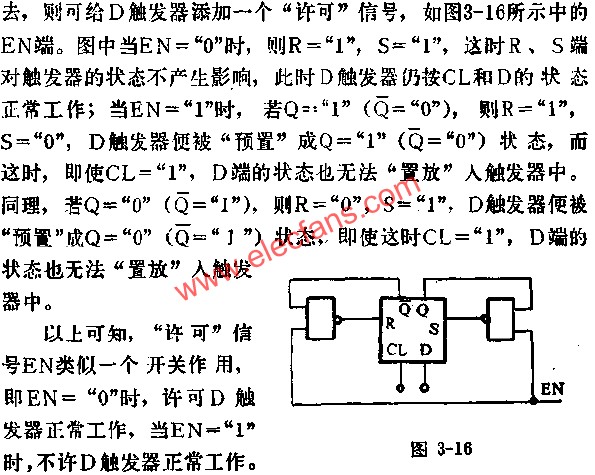

D觸發(fā)器加“許可”信號(hào)電路圖

從D觸發(fā)器的真值表可知,當(dāng)時(shí)鐘脈沖CL="1"時(shí),數(shù)據(jù)輸入端D的狀態(tài)會(huì)被“置放”入觸發(fā)器中去,而與觸發(fā)器原狀無關(guān)。如果當(dāng)時(shí)鐘沖CL="1",D端狀態(tài)不旋轉(zhuǎn)放入

2010-09-21 01:27:59 577

577

577

577

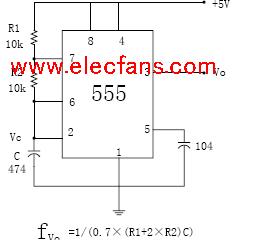

D觸發(fā)器組成環(huán)形計(jì)數(shù)器電路圖

圖中所示是用CMOS電路D觸發(fā)器組成的十進(jìn)制環(huán)形計(jì)數(shù)器.圖中先將D觸發(fā)器拼成移位寄存器,然后把最后一級(jí)D觸發(fā)器

2010-09-20 23:46:58 17358

17358

17358

17358

D觸發(fā)器組成T和J-K觸發(fā)器電路圖

圖中所示是用CMOS電路D觸發(fā)器組成T型觸發(fā)器和J-K觸發(fā)器線路。圖示線路將D觸發(fā)器的Q端與D端相連,就可組成T

2010-09-20 03:31:35 15895

15895

15895

15895觸發(fā)器的分類, 觸發(fā)器的電路

觸發(fā)器的分類, 觸發(fā)器的電路

雙穩(wěn)態(tài)器件有兩類:一類是觸發(fā)器,一類是鎖存器。鎖存器是觸發(fā)器的原始形式?;?/div>

2010-03-09 09:59:59 1491

1491

1491

1491D觸發(fā)器,D觸發(fā)器是什么意思

D觸發(fā)器,D觸發(fā)器是什么意思

邊沿D 觸發(fā)器: 電平觸發(fā)的主從觸發(fā)器工作時(shí),必須在正跳沿前加入輸入信號(hào)。如果在CP 高

2010-03-08 13:53:13 4130

4130

4130

4130T觸發(fā)器,什么是T觸發(fā)器,T觸發(fā)器的邏輯符號(hào)

T觸發(fā)器,什么是T觸發(fā)器

在數(shù)字電路中,凡在CP時(shí)鐘脈沖控制下,根據(jù)輸入信號(hào)T取值的不同,具有保持和翻轉(zhuǎn)功能的電路,即當(dāng)T=0時(shí)

2009-09-30 18:26:07 26472

26472

26472

26472

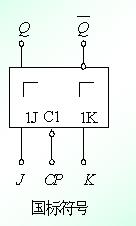

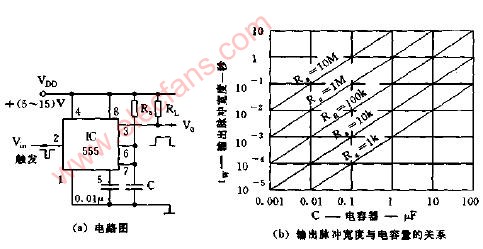

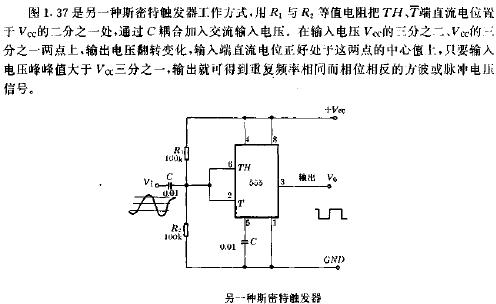

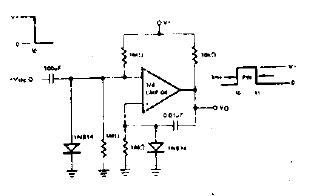

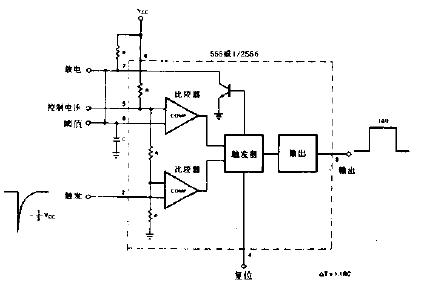

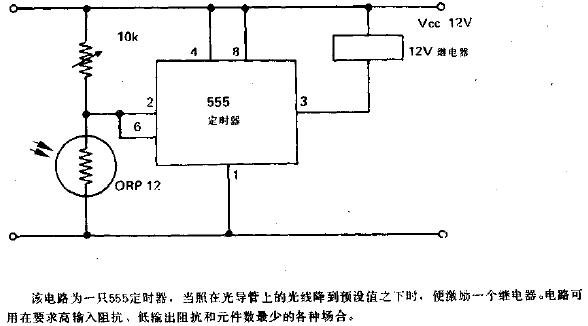

單穩(wěn)態(tài)觸發(fā)器電路圖

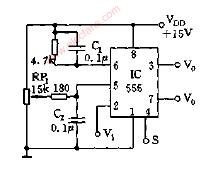

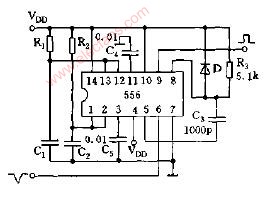

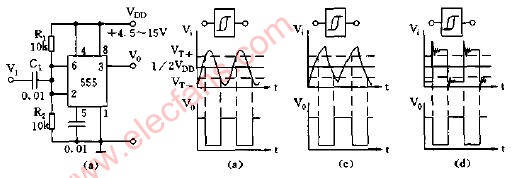

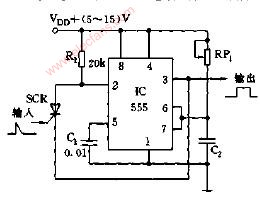

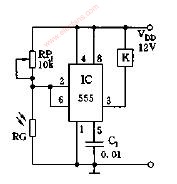

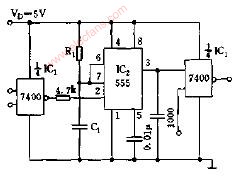

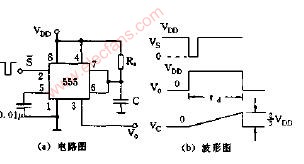

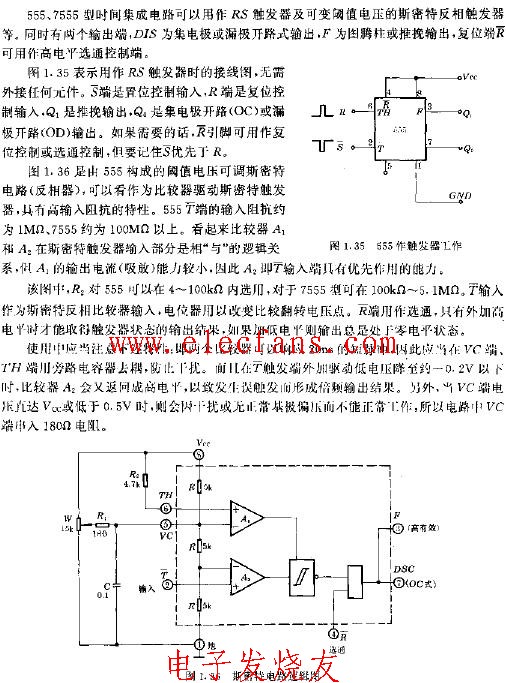

1. 555單穩(wěn)態(tài)觸發(fā)器

圖3.10 單穩(wěn)態(tài)觸發(fā)器電路圖

2008-09-22 11:31:17 2809

2809

2809

2809

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論