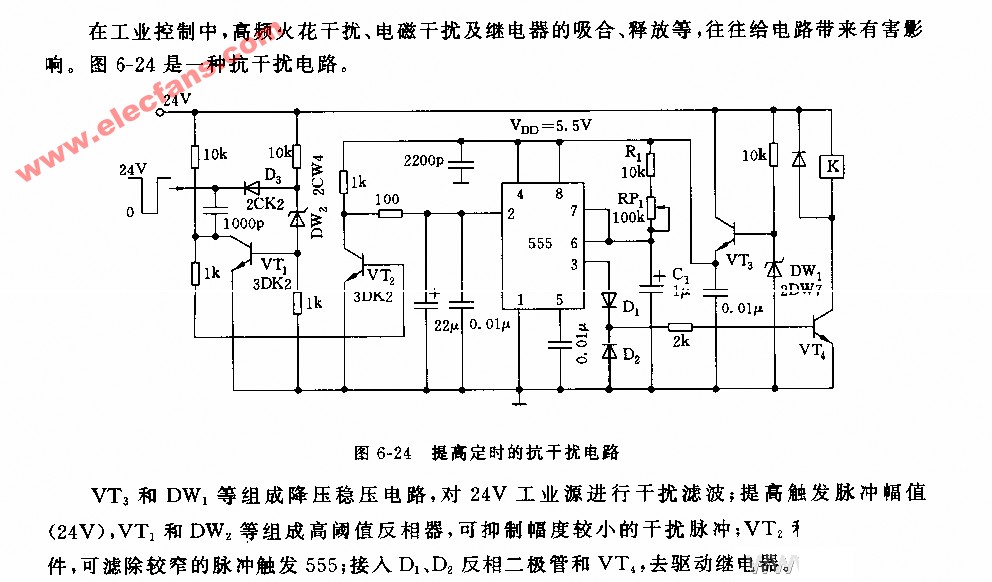

提高定時(shí)的抗干擾電路圖

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

-

電路圖

+關(guān)注

關(guān)注

10316文章

10717瀏覽量

527205

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

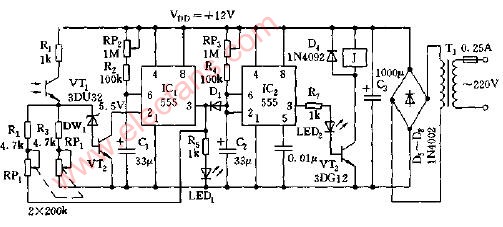

采用555時(shí)基的抗干擾定時(shí)器電路設(shè)計(jì)

在運(yùn)用555時(shí)基電路設(shè)計(jì)而成的定時(shí)器電路中,一般都將555時(shí)基電路連接成單穩(wěn)態(tài)觸 發(fā)器,這樣連接使得電路設(shè)計(jì)簡(jiǎn)單,只需要幾個(gè)電阻器和電容器就

發(fā)表于 10-08 09:12

?5292次閱讀

高速電路的抗干擾設(shè)計(jì)

和濾波。這樣既減少了自身的噪聲也能夠吸收外部對(duì)其的影響,提高自身的抗干擾能力。圖1 簡(jiǎn)要說明在各個(gè)電路階段所產(chǎn)生的噪聲。圖1 各個(gè)

發(fā)表于 09-12 15:01

提高系統(tǒng)的抗干擾能力

抗干擾設(shè)計(jì)的基本任務(wù)是系統(tǒng)或裝置既不因外界電磁干擾影響而誤動(dòng)作或喪失功能,也不向外界發(fā)送過大的噪聲干擾,以免影響其他系統(tǒng)或裝置正常工作。因此提高系統(tǒng)的

發(fā)表于 11-11 06:57

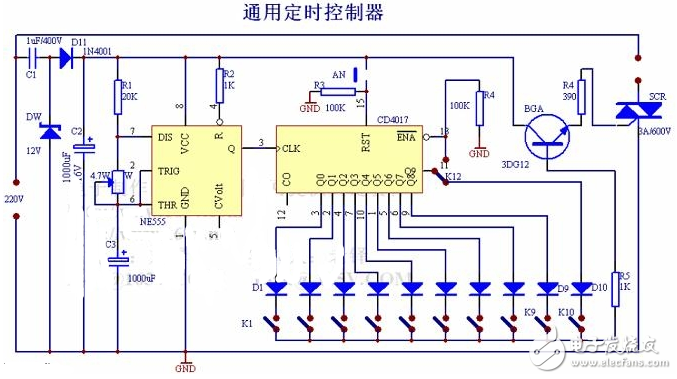

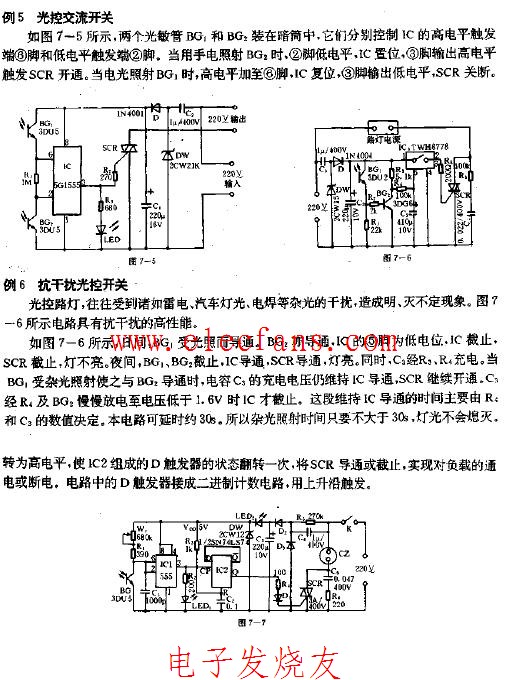

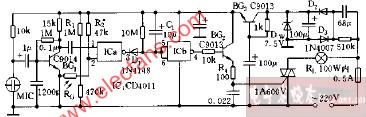

簡(jiǎn)單定時(shí)電路圖大全(計(jì)數(shù)器CD4029\TC9160\CD4017\繼電器)

定時(shí)電路圖、開機(jī)定時(shí)器電路圖、提高抗干擾性能的定時(shí)電路圖

發(fā)表于 05-07 12:42

?5.3w次閱讀

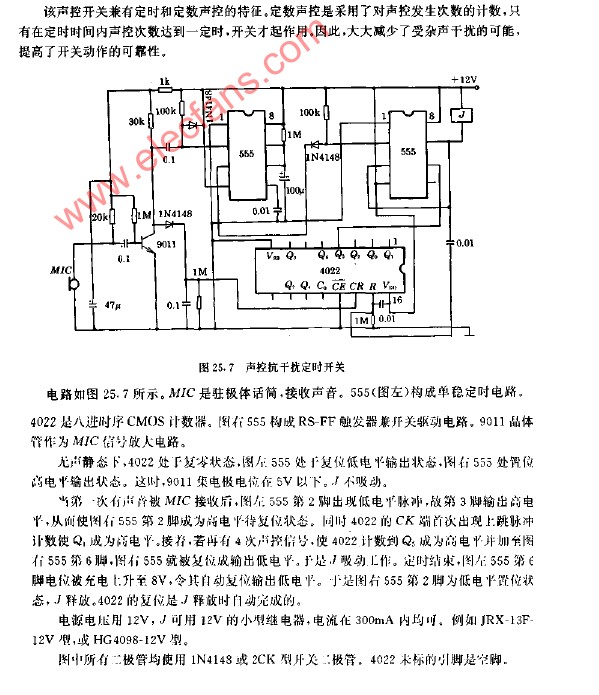

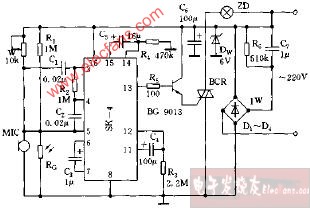

提高定時(shí)的抗干擾電路圖

提高定時(shí)的抗干擾電路圖

評(píng)論