可編程ASIC

相關(guān)推薦

光纖收發(fā)器的特點(diǎn)

采用專用ASIC芯片實(shí)現(xiàn)數(shù)據(jù)線速轉(zhuǎn)發(fā)。可編程ASIC將多項(xiàng)功能集中到一個(gè)芯片上,具有設(shè)計(jì)簡(jiǎn)單、可靠性高、電源消耗少等優(yōu)點(diǎn),能使設(shè)備得到更高的性能和更低的成本。

2023-05-18 16:07:19 154

154

154

154回應(yīng)光纖收發(fā)器特點(diǎn)

這一話題展開介紹。 光纖收發(fā)器特點(diǎn)通常具有以下: 1. 提供超低時(shí)延的數(shù)據(jù)傳輸。 2. 對(duì)網(wǎng)絡(luò)協(xié)議完全透明。 3. 采用專用ASIC芯片實(shí)現(xiàn)數(shù)據(jù)線速轉(zhuǎn)發(fā)。可編程ASIC將多項(xiàng)功能集中到一個(gè)芯片上,具有設(shè)計(jì)簡(jiǎn)單、可靠性高、電源消耗少等優(yōu)

2023-03-31 10:40:15 59

59

59

59可編程電源的原理 可編程電源的優(yōu)缺點(diǎn)

可編程電源是一種可以通過計(jì)算機(jī)編程來控制電源輸出的電源。它可以根據(jù)用戶的需求,自動(dòng)調(diào)節(jié)電源的輸出電壓和電流,從而滿足用戶的需求。可編程電源具有節(jié)能、穩(wěn)定性好、可靠性高等優(yōu)點(diǎn),是一種非常有效的電源。

2023-02-21 15:16:42 1253

1253

1253

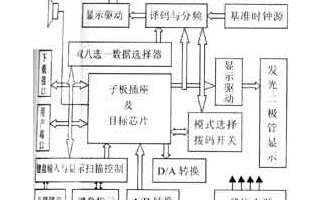

1253基于FPGA的空調(diào)控制畢業(yè)設(shè)計(jì)資料下載

設(shè)計(jì)專用集成電路(ASIC)芯片,而且希望ASIC的設(shè)計(jì)周期盡可能短,最好是在實(shí)驗(yàn)室里就能設(shè)計(jì)出合適的ASIC芯片,并且立即投入實(shí)際應(yīng)用之中,因而出現(xiàn)了現(xiàn)場(chǎng)可編程邏輯器件(FPLD),其中應(yīng)用最廣

2009-10-22 11:36:57

#硬聲創(chuàng)作季 #ASIC 可編程ASIC設(shè)計(jì)-09.02認(rèn)識(shí)openCL加速圖像處理算法過程

asicIC設(shè)計(jì)OpenCL集成電路工藝

水管工發(fā)布于 2022-09-25 05:15:27

#硬聲創(chuàng)作季 #ASIC 可編程ASIC設(shè)計(jì)-09.01Opencl的開發(fā)流程

asicIC設(shè)計(jì)OpenCL集成電路工藝

水管工發(fā)布于 2022-09-25 05:14:34

#硬聲創(chuàng)作季 #ASIC 可編程ASIC設(shè)計(jì)-08.02可編程ASIC設(shè)計(jì)

asicIC設(shè)計(jì)集成電路工藝

水管工發(fā)布于 2022-09-25 05:14:01

#硬聲創(chuàng)作季 #ASIC 可編程ASIC設(shè)計(jì)-08.01HPS介紹

asicIC設(shè)計(jì)集成電路工藝

水管工發(fā)布于 2022-09-25 05:13:27

#硬聲創(chuàng)作季 #ASIC 可編程ASIC設(shè)計(jì)-07.02NiosII處理器系統(tǒng)案例-1

asicIC設(shè)計(jì)NIOSNIOSII集成電路工藝

水管工發(fā)布于 2022-09-25 05:12:23

#硬聲創(chuàng)作季 #ASIC 可編程ASIC設(shè)計(jì)-07.01NiosII軟核處理器

asicIC設(shè)計(jì)NIOSNIOSII集成電路工藝

水管工發(fā)布于 2022-09-25 05:11:51

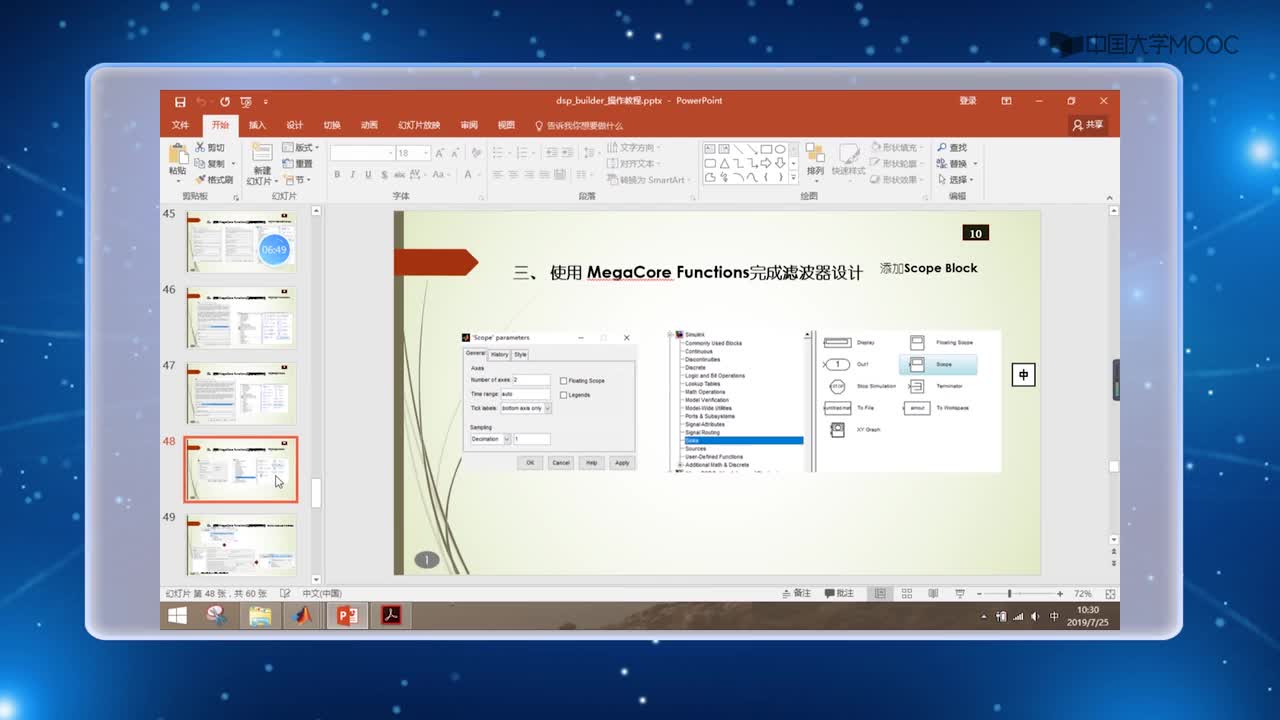

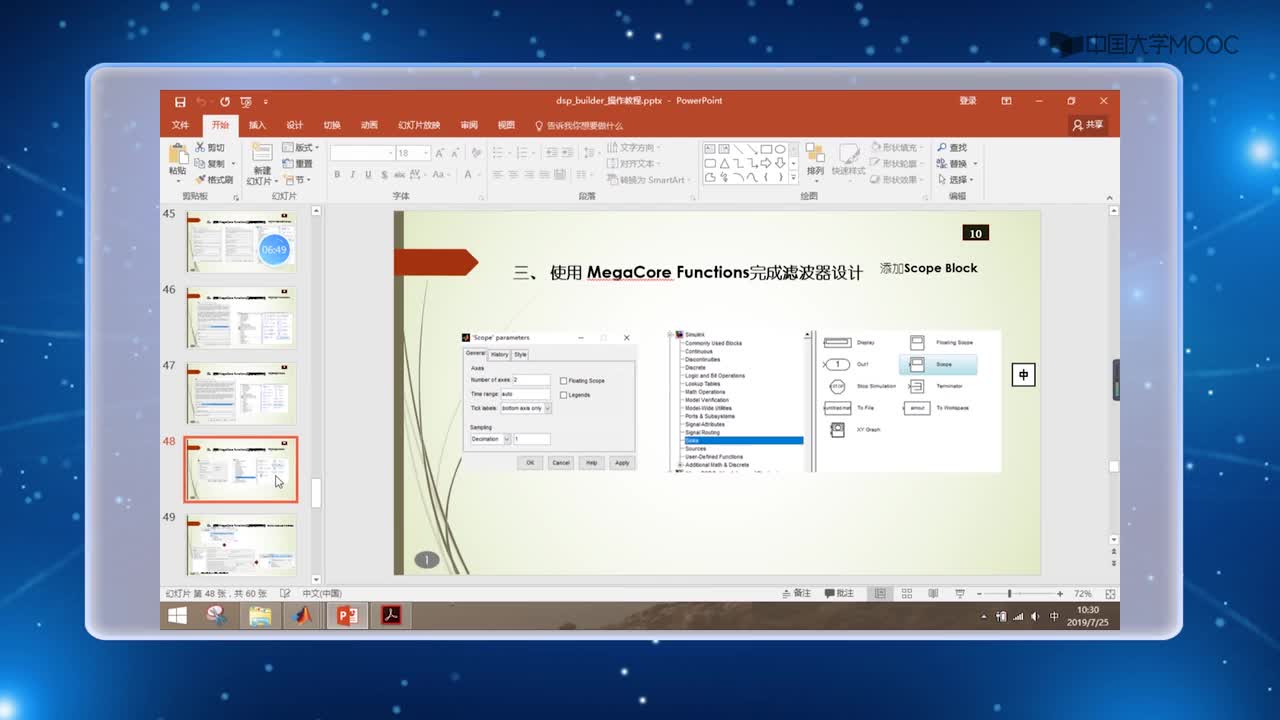

#硬聲創(chuàng)作季 #ASIC 可編程ASIC設(shè)計(jì)-06.04FIR濾波器的項(xiàng)目-2

asicIC設(shè)計(jì)FIR集成電路工藝

水管工發(fā)布于 2022-09-25 05:11:19

#硬聲創(chuàng)作季 #ASIC 可編程ASIC設(shè)計(jì)-06.04FIR濾波器的項(xiàng)目-1

asicIC設(shè)計(jì)FIR集成電路工藝

水管工發(fā)布于 2022-09-25 05:10:47

#硬聲創(chuàng)作季 #ASIC 可編程ASIC設(shè)計(jì)-06.03設(shè)計(jì)模型在FPGA上實(shí)現(xiàn)

fpgaasicIC設(shè)計(jì)

水管工發(fā)布于 2022-09-25 05:10:18

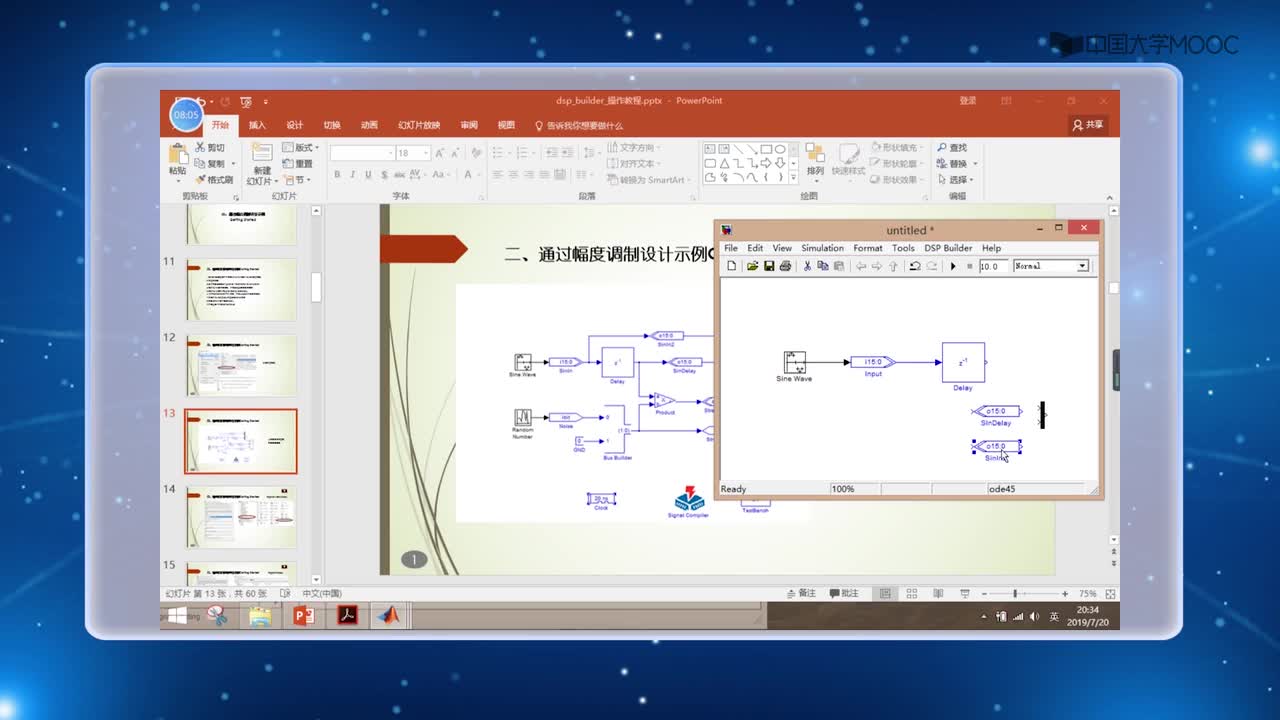

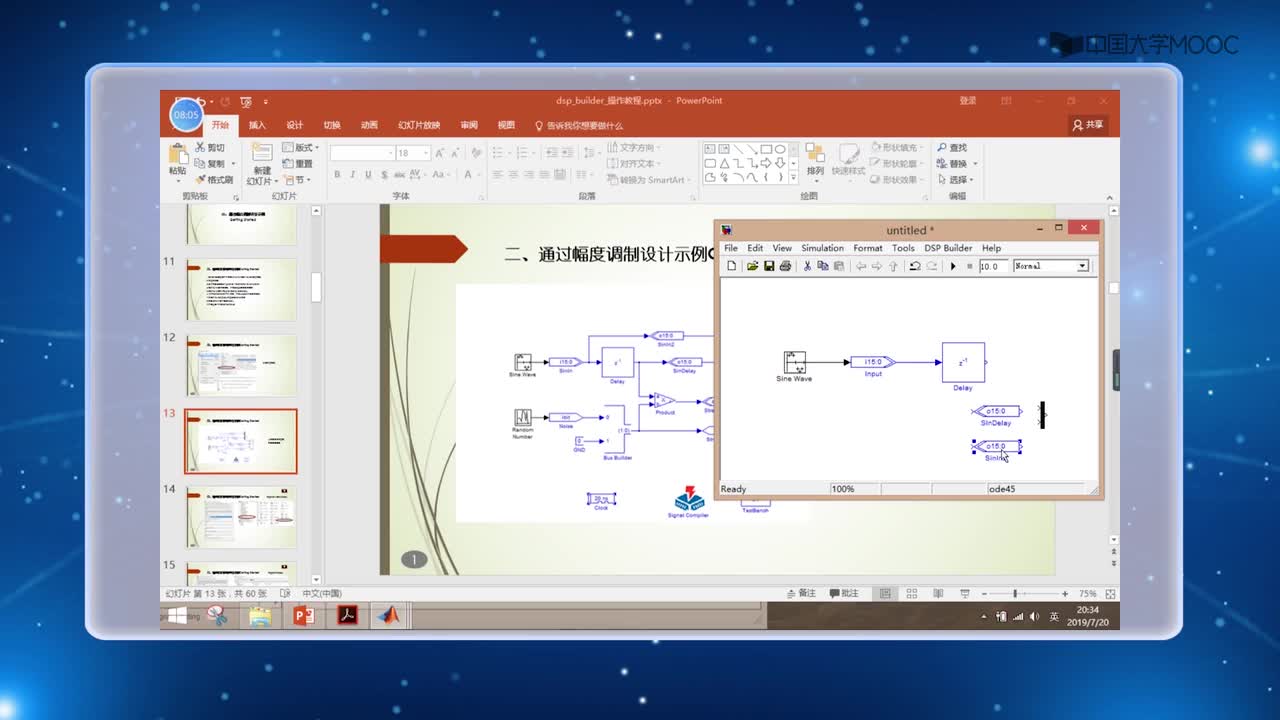

#硬聲創(chuàng)作季 #ASIC 可編程ASIC設(shè)計(jì)-06.02如何完成simulink中建模-2

asicIC設(shè)計(jì)建模SimulinkSimul集成電路工藝

水管工發(fā)布于 2022-09-25 05:09:45

#硬聲創(chuàng)作季 #ASIC 可編程ASIC設(shè)計(jì)-06.02如何完成simulink中建模-1

asicIC設(shè)計(jì)建模SimulinkSimul集成電路工藝

水管工發(fā)布于 2022-09-25 05:09:13

#硬聲創(chuàng)作季 #ASIC 可編程ASIC設(shè)計(jì)-06.01DSP Builder設(shè)計(jì)流程

asicIC設(shè)計(jì)集成電路工藝

水管工發(fā)布于 2022-09-25 05:08:40

#硬聲創(chuàng)作季 #ASIC 可編程ASIC設(shè)計(jì)-05.03.03有限狀態(tài)機(jī)的設(shè)計(jì)2-3

asicIC設(shè)計(jì)集成電路工藝

水管工發(fā)布于 2022-09-25 05:08:10

#硬聲創(chuàng)作季 #ASIC 可編程ASIC設(shè)計(jì)-05.03.02有限狀態(tài)機(jī)的設(shè)計(jì)2-2

asicIC設(shè)計(jì)集成電路工藝

水管工發(fā)布于 2022-09-25 05:07:43

#硬聲創(chuàng)作季 #ASIC 可編程ASIC設(shè)計(jì)-05.03.01有限狀態(tài)機(jī)的設(shè)計(jì)2-1

asicIC設(shè)計(jì)集成電路工藝

水管工發(fā)布于 2022-09-25 05:07:12

#硬聲創(chuàng)作季 #ASIC 可編程ASIC設(shè)計(jì)-05.02有限狀態(tài)機(jī)的設(shè)計(jì)1

asicIC設(shè)計(jì)集成電路工藝

水管工發(fā)布于 2022-09-25 05:06:32

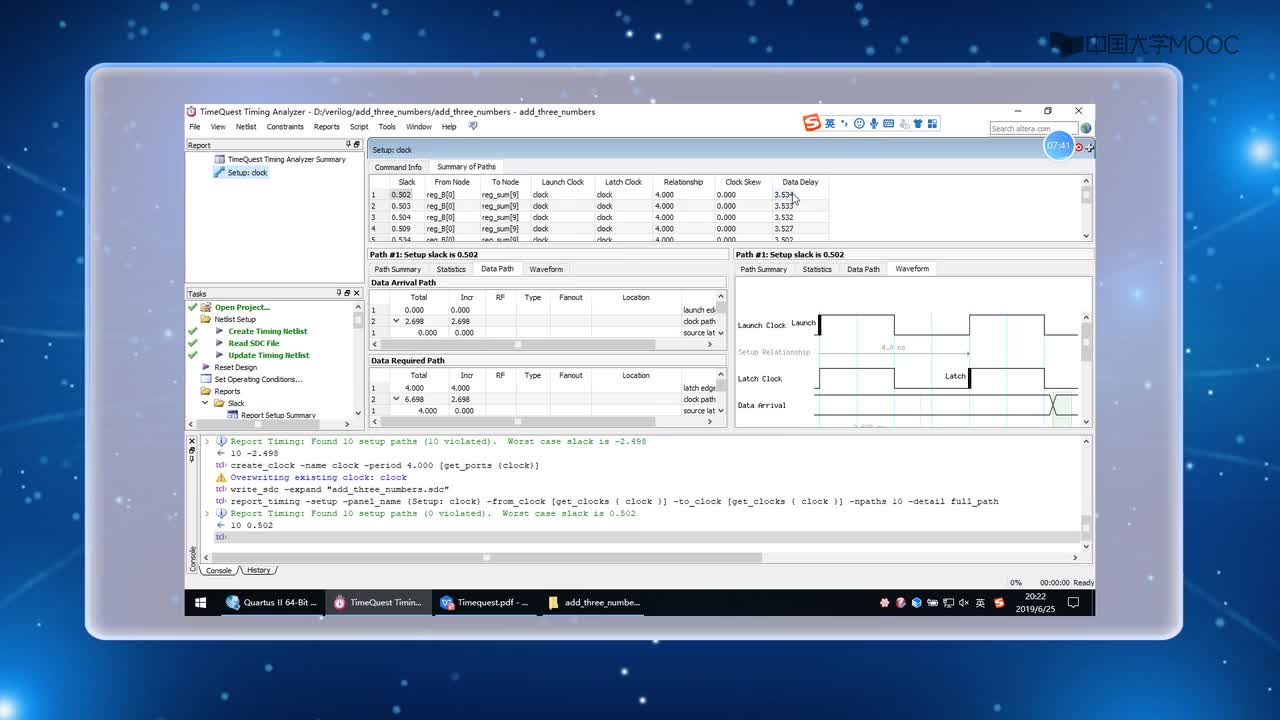

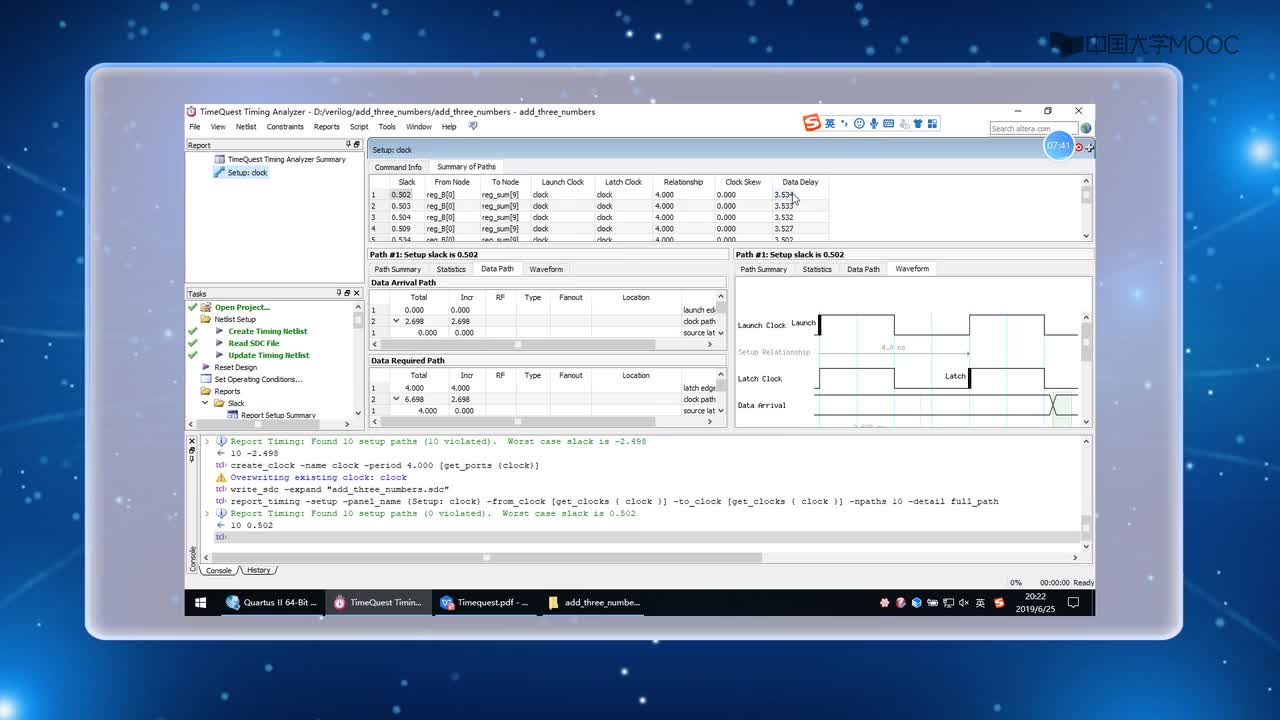

#硬聲創(chuàng)作季 #ASIC 可編程ASIC設(shè)計(jì)-05.01.02Quartus ii中時(shí)序分析工具的使用2-2

asicIC設(shè)計(jì)時(shí)序時(shí)序分析QUARTUS II集成電路工藝

水管工發(fā)布于 2022-09-25 05:05:54

#硬聲創(chuàng)作季 #ASIC 可編程ASIC設(shè)計(jì)-05.01.02Quartus ii中時(shí)序分析工具的使用2-1

asicIC設(shè)計(jì)時(shí)序時(shí)序分析QUARTUS II集成電路工藝

水管工發(fā)布于 2022-09-25 05:05:23

#硬聲創(chuàng)作季 #ASIC 可編程ASIC設(shè)計(jì)-05.01.01Quartus ii中時(shí)序分析工具的使用1

asicIC設(shè)計(jì)時(shí)序時(shí)序分析QUARTUS II集成電路工藝

水管工發(fā)布于 2022-09-25 05:04:52

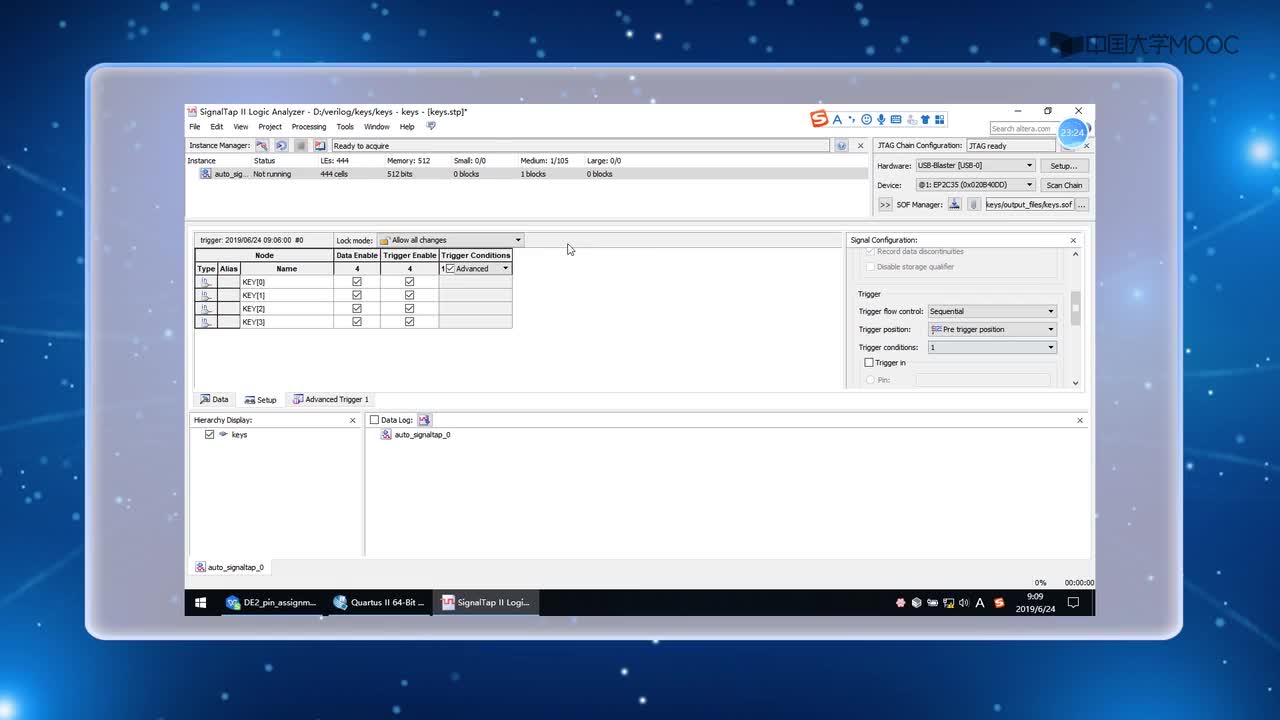

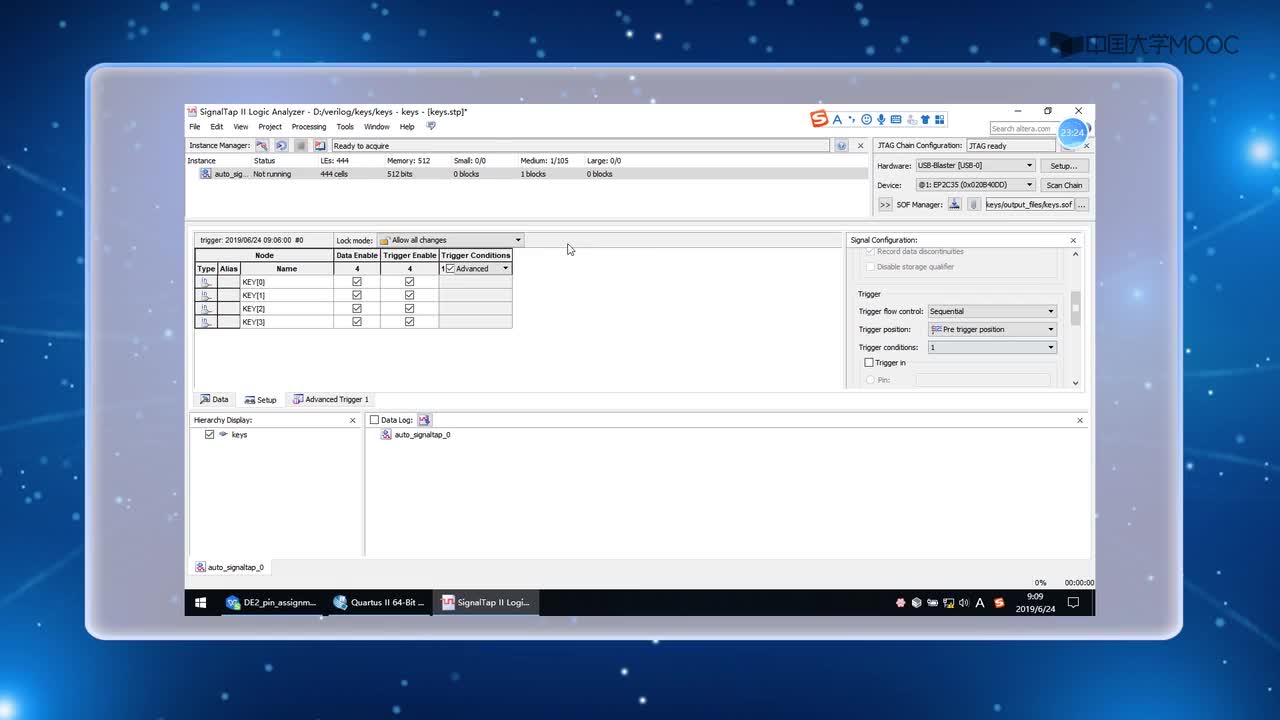

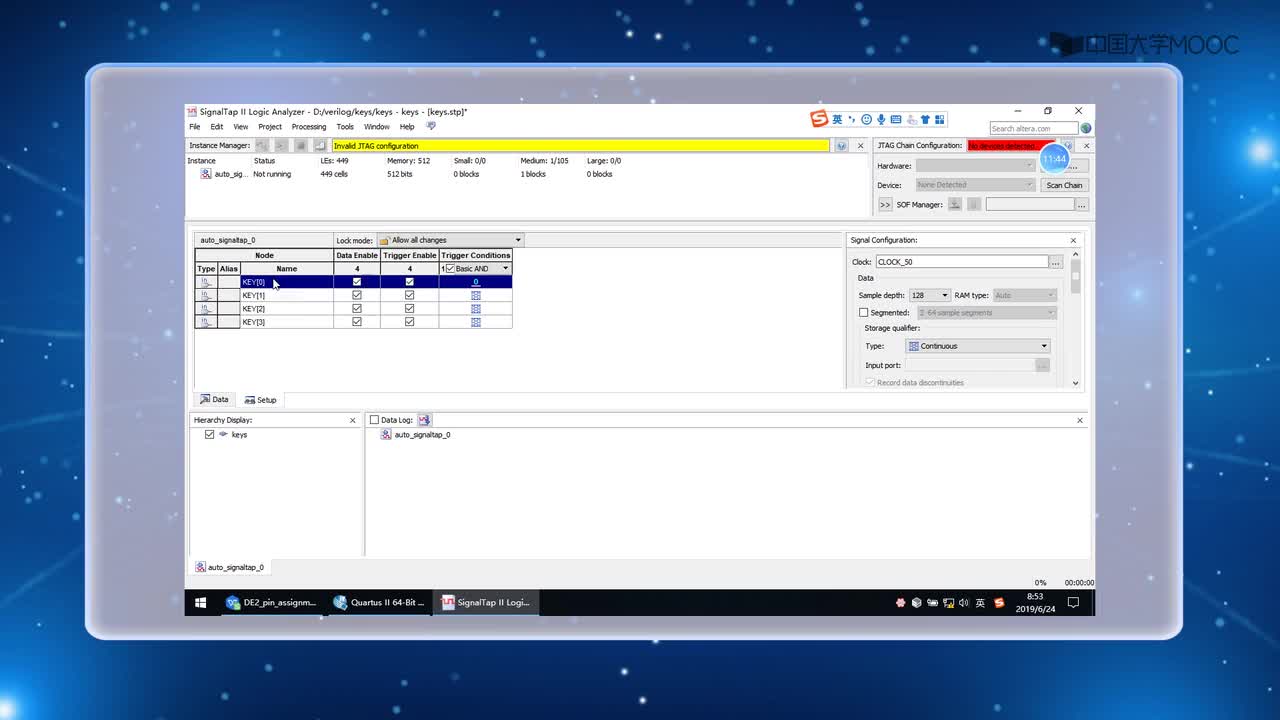

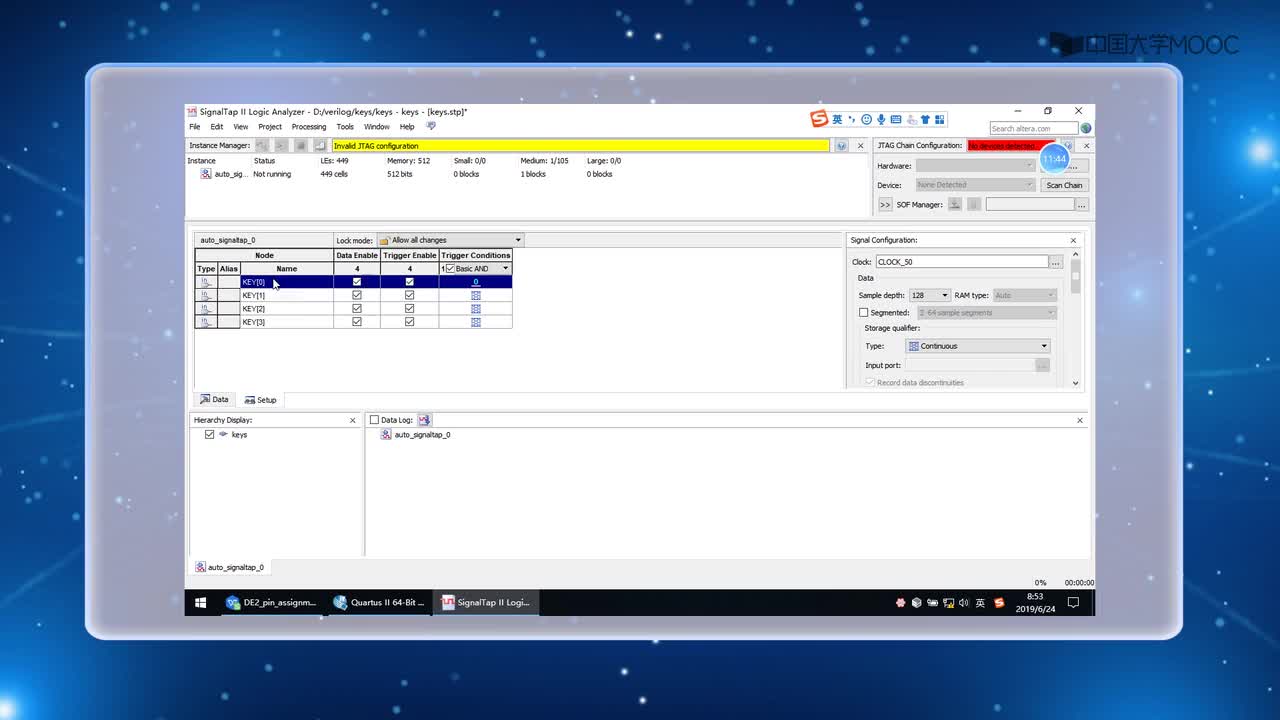

#硬聲創(chuàng)作季 #ASIC 可編程ASIC設(shè)計(jì)-04.04.02singal configuration的高級(jí)設(shè)

asicIC設(shè)計(jì)gal集成電路工藝

水管工發(fā)布于 2022-09-25 05:04:20

#硬聲創(chuàng)作季 #ASIC 可編程ASIC設(shè)計(jì)-04.04.02singal configuration的高級(jí)設(shè)

asicIC設(shè)計(jì)gal集成電路工藝

水管工發(fā)布于 2022-09-25 05:03:48

#硬聲創(chuàng)作季 #ASIC 可編程ASIC設(shè)計(jì)-04.04.02singal configuration的高級(jí)設(shè)

asicIC設(shè)計(jì)gal集成電路工藝

水管工發(fā)布于 2022-09-25 05:03:20

#硬聲創(chuàng)作季 #ASIC 可編程ASIC設(shè)計(jì)-04.04.01singal configuration的高級(jí)設(shè)

asicIC設(shè)計(jì)gal集成電路工藝

水管工發(fā)布于 2022-09-25 05:02:39

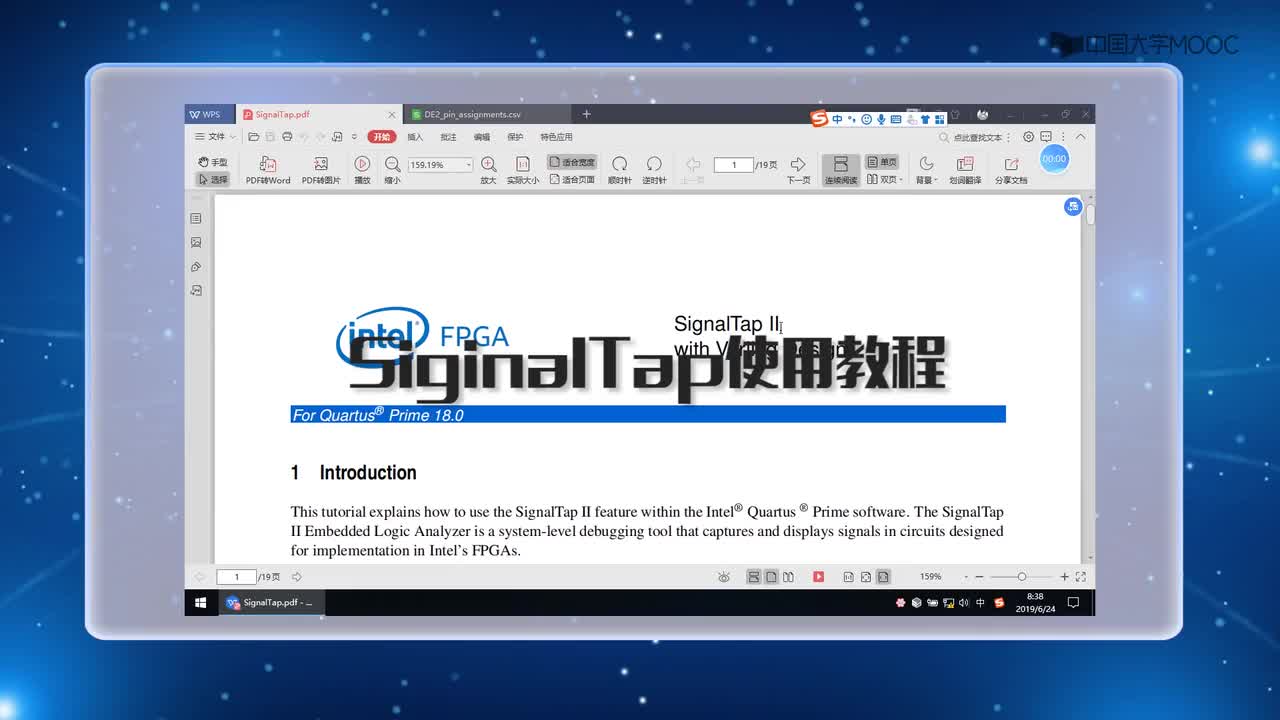

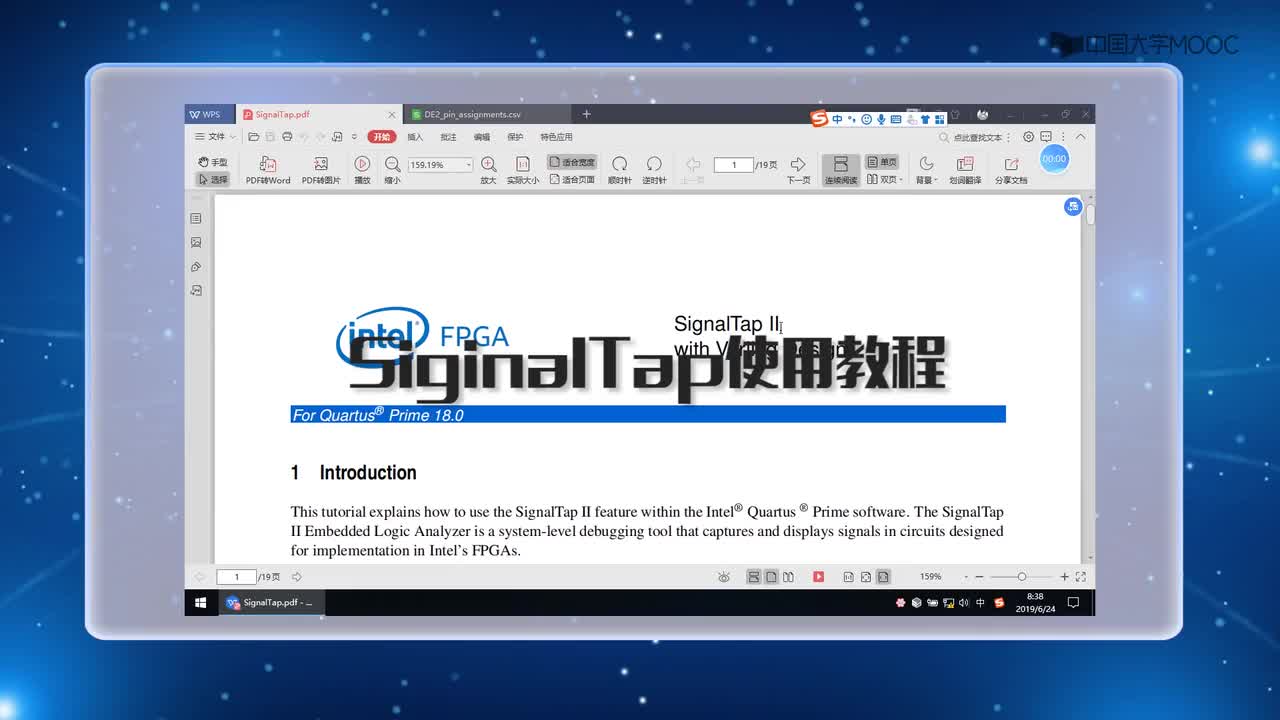

#硬聲創(chuàng)作季 #ASIC 可編程ASIC設(shè)計(jì)-04.03Quartus II的驗(yàn)證及調(diào)試工具

asicIC設(shè)計(jì)QUARTUS II集成電路工藝

水管工發(fā)布于 2022-09-25 05:02:08

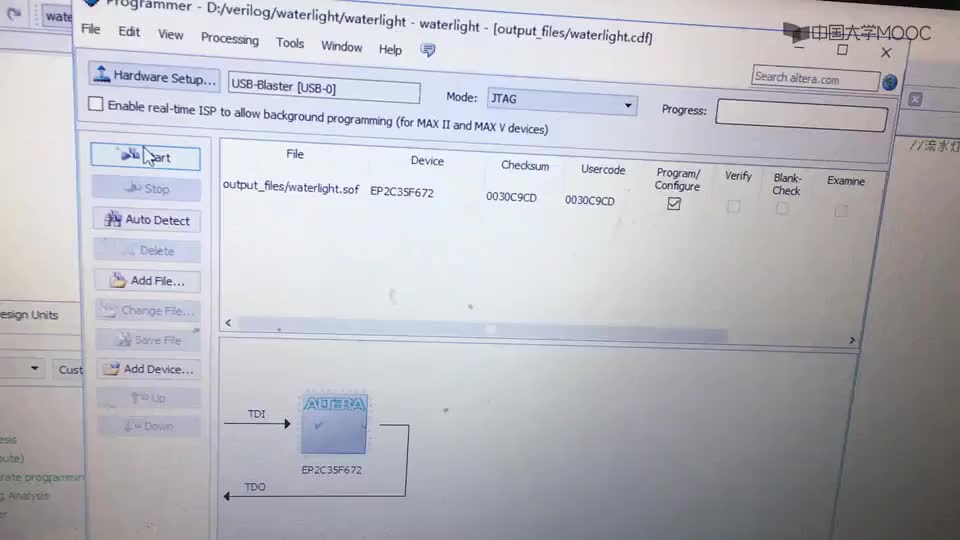

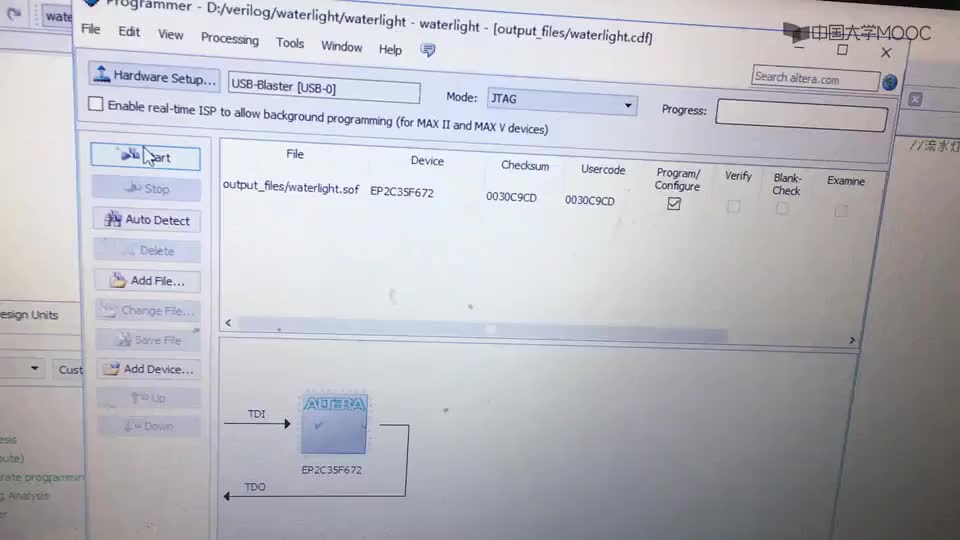

#硬聲創(chuàng)作季 #ASIC 可編程ASIC設(shè)計(jì)-04.02Quartus II的下載驗(yàn)證

asicIC設(shè)計(jì)QUARTUS II集成電路工藝

水管工發(fā)布于 2022-09-25 05:01:36

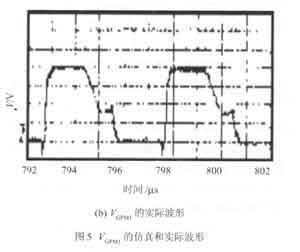

#硬聲創(chuàng)作季 #ASIC 可編程ASIC設(shè)計(jì)-04.01FPGA設(shè)計(jì)中的仿真方法

fpgaasic

水管工發(fā)布于 2022-09-25 05:01:09

#硬聲創(chuàng)作季 #ASIC 可編程ASIC設(shè)計(jì)-03.03Verilog HDL建模實(shí)例

asicIC設(shè)計(jì)建模Verilog HDL集成電路工藝

水管工發(fā)布于 2022-09-25 05:00:30

#硬聲創(chuàng)作季 #ASIC 可編程ASIC設(shè)計(jì)-03.02Verilog HDL基本語(yǔ)法(二)

asicIC設(shè)計(jì)Verilog HDL集成電路工藝

水管工發(fā)布于 2022-09-25 04:59:57

#硬聲創(chuàng)作季 #ASIC 可編程ASIC設(shè)計(jì)-03.01Verilog HDL基本語(yǔ)法(一)

asicIC設(shè)計(jì)Verilog HDL集成電路工藝

水管工發(fā)布于 2022-09-25 04:59:26

#硬聲創(chuàng)作季 #ASIC 可編程ASIC設(shè)計(jì)-02.04FPGA的分配與驗(yàn)證-2

fpgaasic

水管工發(fā)布于 2022-09-25 04:58:55

#硬聲創(chuàng)作季 #ASIC 可編程ASIC設(shè)計(jì)-02.04FPGA的分配與驗(yàn)證-1

fpgaasic

水管工發(fā)布于 2022-09-25 04:58:14

#硬聲創(chuàng)作季 #ASIC 可編程ASIC設(shè)計(jì)-02.03EDA設(shè)計(jì)工具(二)

asicEDA工具

水管工發(fā)布于 2022-09-25 04:57:45

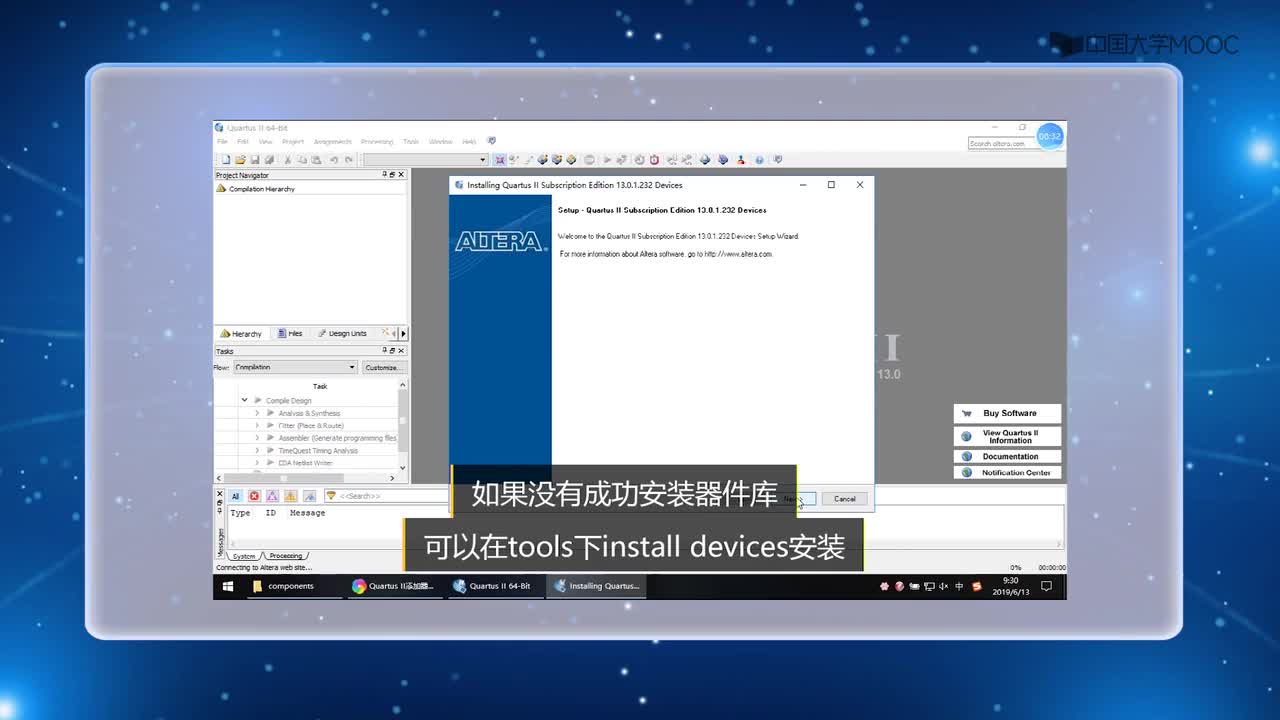

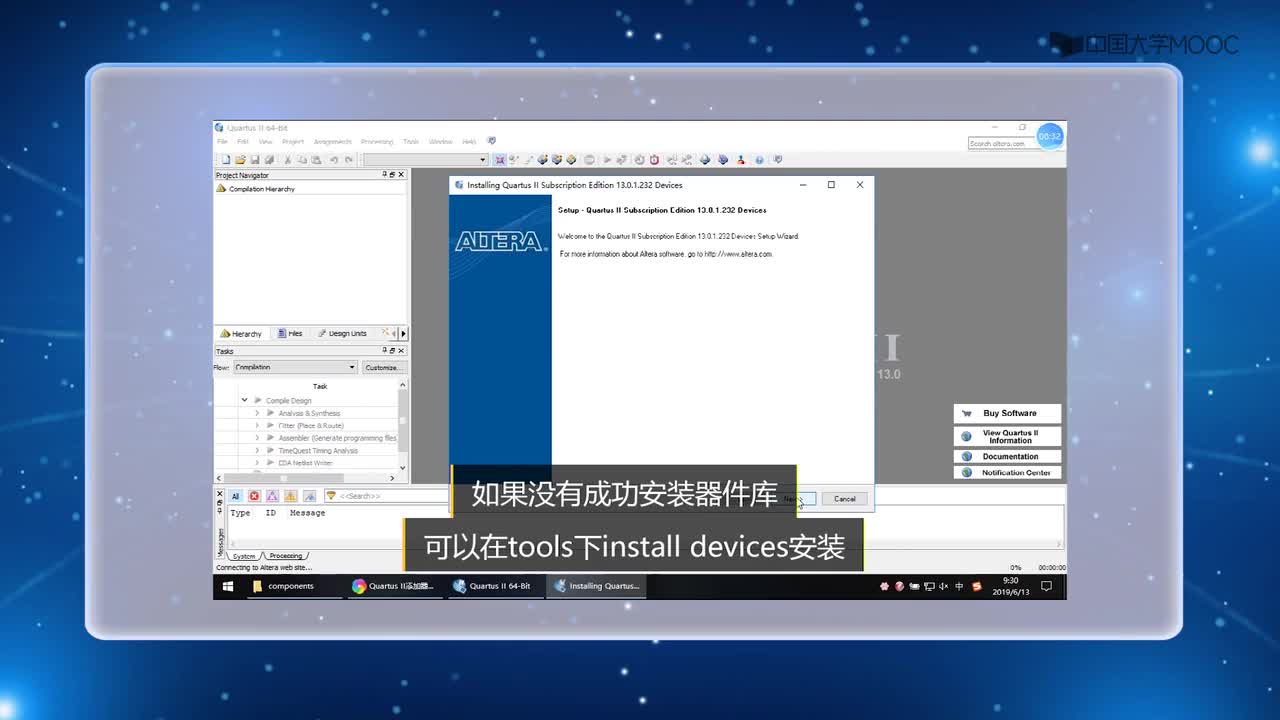

#硬聲創(chuàng)作季 #ASIC 可編程ASIC設(shè)計(jì)-02.02EDA設(shè)計(jì)工具(一)-2

asicEDA工具

水管工發(fā)布于 2022-09-25 04:57:16

#硬聲創(chuàng)作季 #ASIC 可編程ASIC設(shè)計(jì)-02.02EDA設(shè)計(jì)工具(一)-1

asicEDA工具

水管工發(fā)布于 2022-09-25 04:56:48

#硬聲創(chuàng)作季 #ASIC 可編程ASIC設(shè)計(jì)-02.01DE2開發(fā)板資源

asicIC設(shè)計(jì)集成電路工藝

水管工發(fā)布于 2022-09-25 04:56:18

#硬聲創(chuàng)作季 #ASIC 可編程ASIC設(shè)計(jì)-01.04DE2開發(fā)板上FPGA

fpgaasic開發(fā)板

水管工發(fā)布于 2022-09-25 04:55:47

#硬聲創(chuàng)作季 #ASIC 可編程ASIC設(shè)計(jì)-01.02集成電路設(shè)計(jì)方法

asicIC設(shè)計(jì)集成電路工藝

水管工發(fā)布于 2022-09-25 04:54:42

#硬聲創(chuàng)作季 #ASIC 可編程ASIC設(shè)計(jì)-01.01集成電路和可編程ASIC

asicIC設(shè)計(jì)集成電路工藝

水管工發(fā)布于 2022-09-25 04:54:04

如何使用GreenPAK SLG46537V IC等可編程ASIC來開發(fā)AVR

自動(dòng)電壓調(diào)節(jié)器(AVR)通常也稱為穩(wěn)壓器,它通過補(bǔ)償輸入電壓的波動(dòng)來調(diào)節(jié)供電電壓電平,在許多工業(yè)和住宅應(yīng)用中都很常見。例如,AVR被用于船舶發(fā)電機(jī)組、應(yīng)急電源和石油鉆井平臺(tái),以在電力需求波動(dòng)期間穩(wěn)定電壓電平。

2022-07-10 11:26:40 763

763

763

763片上可編程系統(tǒng)原理及應(yīng)用

片上可編程系統(tǒng)SOPC是一種靈活、高效的SoC解決方案,而FPGA 是可編程再設(shè)計(jì)的“萬(wàn)能”芯片,F(xiàn)PGA是作為專用集成電路(ASIC)領(lǐng)域中的一種半定制電路而出現(xiàn)的,在硅片上預(yù)先設(shè)計(jì)實(shí)現(xiàn)的具有可編程特性的集成電路,未來的FPGA芯片密度不斷提高。

2021-10-01 09:07:00 1454

1454

1454

1454Socionext 選用Flex Logix嵌入式eFPGA用于5G無(wú)線基站平臺(tái)

7nm ASIC 項(xiàng)目開發(fā) 。通過利用eFPGA,Socionext可為客戶提供可編程ASIC,即在流片后也能進(jìn)行再配置,滿足新要求并根據(jù)需求改變標(biāo)準(zhǔn)和協(xié)議。 通過集成 FPGA,Socionext

2021-07-02 17:06:23 959

959

959

959Socionext選用Flex Logix嵌入式eFPGA用于5G無(wú)線基站平臺(tái)

7nm ASIC 項(xiàng)目開發(fā) 。通過利用eFPGA,Socionext可為客戶提供可編程ASIC,即在流片后也能進(jìn)行再配置,滿足新要求并根據(jù)需求改變標(biāo)準(zhǔn)和協(xié)議。

2021-06-29 16:40:53 10304

10304

10304

10304Socionext將選用Flex Logix嵌入式eFPGA用于5G無(wú)線基站平臺(tái)

,Socionext可為客戶提供可編程ASIC,即在流片后也能進(jìn)行再配置,滿足新要求并根據(jù)需求改變標(biāo)準(zhǔn)和協(xié)議。 通過集成 FPGA,Socionext可通過消除基站中的單顆芯片來提高性能并降低功耗。這為運(yùn)營(yíng)商

2021-06-25 10:47:58 1536

1536

1536

1536現(xiàn)場(chǎng)可編程門陣列簡(jiǎn)介

FPGA業(yè)界的可編程只讀存儲(chǔ)器(PROM)和可編程邏輯器件(PLD)萌芽。可編程只讀存儲(chǔ)器(PROM)和可編程邏輯器件(PLD)都可以分批在工廠或在現(xiàn)場(chǎng)(現(xiàn)場(chǎng)可編程)編程,然而,可編程邏輯被硬線連接在邏輯門之間。

2021-04-07 10:14:02 76

76

76

76基于CPLD/FPGA器件實(shí)現(xiàn)主從式下載開發(fā)系統(tǒng)的應(yīng)用方案

當(dāng)前在EDA領(lǐng)域,只要具備臺(tái)式或筆記本電腦并裝有工具軟件,就可以方便地對(duì)可編程ASIC(CPLD/FPGA)進(jìn)行設(shè)計(jì)開發(fā),在系統(tǒng)可編程(ISP)器件為我們提供了這種便利條件。ISP方式雖然可以用一根

2020-09-16 20:17:17 502

502

502

502

可編程邏輯器件和ASIC對(duì)比介紹

可編程邏輯器件PLD(Programmable Logic Device)就是一種可以由用戶定義和設(shè)置邏輯功能的數(shù)字集成電路,屬于可編程 ASIC。

2020-09-04 17:02:17 2107

2107

2107

2107可編程邏輯器材有哪些種類

如今出產(chǎn)可編程ASIC 器材的廠家首要有Xilinx、Altera、Lattice、Actel、Atmel、AMD、Cypress、Intel、Motorola、TI等。各廠家又有紛歧樣的系列和商品稱謂,器材構(gòu)造和分類更是紛歧樣,本節(jié)介紹其間幾種比照通行的分類辦法。

2020-06-18 08:54:15 1234

1234

1234

1234如何采用IXP1200網(wǎng)絡(luò)處理器構(gòu)建路由器

網(wǎng)絡(luò)處理器是現(xiàn)代綜合業(yè)務(wù)數(shù)據(jù)網(wǎng)絡(luò)不斷發(fā)展更新的產(chǎn)物,是一種基于可編程 ASIC 結(jié) 構(gòu)的新一代SoC 芯片。它是為了適應(yīng)下一代高速網(wǎng)絡(luò)特點(diǎn),即為了能夠提供Qos,能夠不斷 適應(yīng)新的網(wǎng)絡(luò)應(yīng)用,能夠發(fā)展新的網(wǎng)絡(luò)管理模式以及能夠快速響應(yīng)市場(chǎng)對(duì)新的網(wǎng)絡(luò)功能的需 求而推出的一種新的芯片產(chǎn)品。

2019-01-15 08:05:00 1346

1346

1346

1346

探析FPGA和ASIC的原理和區(qū)別

FPGA是可編程ASIC。 ASIC:專用集成電路,它是面向?qū)iT用途的電路,專門為一個(gè)用戶設(shè)計(jì)和制造的。

2018-12-15 09:58:46 5032

5032

5032

5032FPGA的發(fā)展?fàn)顩r和趨勢(shì)發(fā)展方向及器件與EDA的發(fā)展和廠商介紹

類產(chǎn)品是由用戶自己而不是由芯片生產(chǎn)廠最后完成其邏輯功能的, 一類產(chǎn)品就是可編程邏輯器件·現(xiàn)在用戶使用可編程ASIC, 借助日益先進(jìn)的E D A 技術(shù), 可以實(shí)現(xiàn)各種數(shù)字電子系統(tǒng)以及功能模塊的調(diào)試, 下面分別闡述。

2018-10-19 16:52:00 14

14

14

14可編程ASIC的I/O細(xì)胞

Input/output cell (I/O cell) ? I/O requirements ? DC output ? AC output ? DC input ? AC input ?Clock input ? Power input。

2016-06-16 17:57:46 15

15

15

15可編程ASIC設(shè)計(jì)軟件_英文資料

The design software is much more closely tied to the FPGA architecture than is the case for other types of ASICs。

2016-06-16 17:57:46 12

12

12

12可編程ASIC互連_英文資料

programmable interconnect ? raw materials: aluminum-based metallization and a line capacitance of 0.2pFcm–1.

2016-06-16 17:57:46 11

11

11

11EDA技術(shù)與可編程ASIC的設(shè)計(jì)實(shí)現(xiàn)

EDA技術(shù)與可編程ASIC的設(shè)計(jì)實(shí)現(xiàn),下來看看。

2016-05-19 15:16:15 13

13

13

13顛覆式革命:解決FPGA掉電易失難題

CPLD與FPGA雖然都?xì)w屬于可編程ASIC器件,但因?yàn)榻Y(jié)構(gòu)上的差異,CPLD使用起來要比FPGA方便很多。CPLD編程采用的是E2PROM或FASTFLASH技術(shù),無(wú)需外部存儲(chǔ)芯片,而FPGA

2015-04-27 17:02:33 8085

8085

8085

8085演講稿:湯立人先生詳解Xilinx首個(gè)ASIC級(jí)可編程架構(gòu)UltraScale

演講稿:湯立人先生詳解Xilinx首個(gè)ASIC級(jí)可編程架構(gòu)UltraScale 行業(yè)首款20nm All Programmable器件; 行業(yè)首個(gè)ASIC級(jí)可編程架構(gòu) ;比同類競(jìng)爭(zhēng)產(chǎn)品提前一年實(shí)現(xiàn)1.5至2倍的性能和集成度

2013-07-09 22:35:10 88

88

88

88常見問題解答:Xilinx采用首個(gè)ASIC級(jí)UltraScale可編程架構(gòu)

Xilinx采用首個(gè)ASIC級(jí)UltraScale可編程架構(gòu)之首款20nm All Programmable器件開始投片常見問題解答:什么是UltraScale 架構(gòu)?ASIC 級(jí) UltraScale 架構(gòu)能為賽靈思 FPGA、3D IC 和 SoC 帶來哪些優(yōu)勢(shì)?

2013-07-09 20:28:52 2035

2035

2035

2035可編程ASIC器件主從式結(jié)構(gòu)開發(fā)系統(tǒng)的設(shè)計(jì)

1 引言

當(dāng)前在EDA領(lǐng)域,只要具備臺(tái)式或筆記本電腦并裝有工具軟件,就可以方便地對(duì)可編程ASIC(CPLD/FPGA)進(jìn)行設(shè)計(jì)開發(fā),在系統(tǒng)可編程(ISP)器件為我們提供了這種便利條件。IS

2010-07-15 10:36:02 564

564

564

564

EDA技術(shù)與可編程ASIC的設(shè)計(jì)實(shí)現(xiàn)

EDA技術(shù)與可編程ASIC的設(shè)計(jì)實(shí)現(xiàn)

集成電路經(jīng)過半個(gè)世紀(jì)的演變,發(fā)展,目前品種已達(dá)5萬(wàn)種,年產(chǎn)量以億塊計(jì).

2010-06-19 09:50:19 24

24

24

24可編程SoC(SoPC),什么是可編程SoC(SoPC)

可編程SoC(SoPC),什么是可編程SoC(SoPC)

SOPC ( System on a Programmable Chip,片上可編程系統(tǒng))是以PLD(可編程邏輯器件)取代ASIC(專用集成電路),更

2010-03-26 17:01:35 2269

2269

2269

2269可編程模擬器件原理與開發(fā)

可編程模擬器件原理與開發(fā)作者:趙曙光陳麗萍 殷延瑞 趙明英關(guān)鍵詞:可編程模擬器件,模擬集成電路,ASIC摘要:可編程模擬器件(Programmable Analog Device)是近年來嶄露頭

2010-02-06 17:05:27 44

44

44

44一種零NRE的可編程ASIC eASIC

在激烈的市場(chǎng)競(jìng)爭(zhēng)中,創(chuàng)新和差異化對(duì)產(chǎn)品的成功至關(guān)重要。為了達(dá)到這一目的,必須尋找能夠價(jià)格合理的IC 解決方案實(shí)現(xiàn)特定的差異化應(yīng)用。

2009-11-30 16:28:54 4

4

4

4可編程ASIC與MCS51單片機(jī)接口設(shè)計(jì)及實(shí)現(xiàn)

針對(duì)可編程ASIC和MCS51單片機(jī)的特點(diǎn),對(duì)兩者之間的接口方式進(jìn)行了分析。用Verilog HDL給出了幾個(gè)實(shí)用的接口參考程序。關(guān)鍵字:可編程ASIC; 單

2009-06-09 08:43:35 15

15

15

15 電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論