(目前超過80多種不同的型號(hào))����,是恩智浦不斷發(fā)展的Cortex-M0+藍(lán)圖中的首款產(chǎn)品。此外���,恩智浦還宣布基于LPC812的mbed/Arduino開發(fā)板LPC800-MAX將于2013年4月發(fā)布�����。

2013-03-06 15:43:45 1952

1952 15G的DSP全套學(xué)習(xí)資料TMS320F2812開發(fā)板 原理圖和PCB設(shè)計(jì)圖紙

2019-03-13 15:12:46

我正在開發(fā)一個(gè) LPC8N04 項(xiàng)目���,并確定我希望總線有兩個(gè)主控�。

我對(duì) LPC 和 MCUExpresso IDE 也很陌生�。

我的 LPC8N04 被用作 EEPROM,但我希望它偶爾從 i2c

2023-05-19 07:12:24

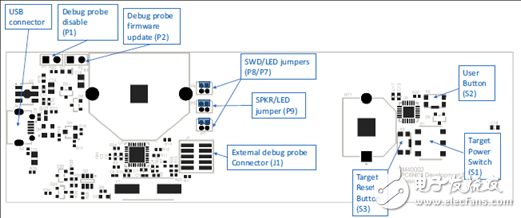

LPC8N04開發(fā)板板載了DAPlink����,其中有虛擬串口功能,可是LPC8N04沒有串口啊�����,那么這個(gè)DAPlink的虛擬串口連接到那里了�����?

2023-11-08 06:06:42

我正在使用 LPC8N04 開發(fā)板(0M40002,修訂版 C)�。直到幾天前,我才能夠調(diào)試和刷新代碼��。探測(cè)器被檢測(cè)到,但是當(dāng)我使用 MCU Expresso 啟動(dòng)調(diào)試時(shí)��,我在 3 個(gè)窗口中收到這些錯(cuò)誤:視窗 1:無法連接探針?biāo)饕?1 的電線��。錯(cuò)誤:電線確認(rèn)故障 - 目標(biāo)已連接�����?

2023-04-12 08:52:27

LPC8N04 勘誤表

2022-12-06 07:43:54

只是想看看是否有人有我可以重復(fù)使用的好的 uart bitbash 片段?

目標(biāo)是 LPC8N04�,所需波特率是 460080�。將用于 Modbus,因此消息可能會(huì)變長(zhǎng)����。

如果有人能指出一個(gè)相關(guān)的好項(xiàng)目,那在我開始之前也很棒��。

2023-05-19 06:17:28

LPC8N04數(shù)據(jù)手冊(cè)

2022-12-06 07:45:21

LPC1102/04 用戶手冊(cè)

2022-12-08 06:50:48

LPC11E6x器件的正確開發(fā)板�。所有其他LPC11Exx器件應(yīng)使用各自產(chǎn)品信息頁面上的相應(yīng)LPC11Exx開發(fā)板。 LPCXpresso是一個(gè)支持基于ARM的微控制器的低成本開發(fā)平臺(tái)���。該平臺(tái)由簡(jiǎn)化的基于Eclipse的IDE和低成本目標(biāo)板組成����,其中包括一個(gè)連接的JTAG調(diào)試器

2019-11-07 08:53:19

介紹LPC1768開發(fā)板下載軟件文章目錄前言軟件包二、軟件內(nèi)選擇1.界面2.讀入數(shù)據(jù)總結(jié)前言LPC1768開發(fā)板下載過程與單片機(jī)下載過程極為相似軟件包鏈接:https://pan.baidu.com

2022-02-07 07:21:15

LPC2138的100M以太網(wǎng)開發(fā)板原理圖.pdf

2016-09-19 08:13:31

LPC2300開發(fā)板資料[hide][/hide]LPC2300的UCOS II

2009-04-18 20:29:41

LPC54608開發(fā)板的助力�,該汽車組合儀表的設(shè)計(jì)效果一定會(huì)令人注目。后面有時(shí)間的話�,定要找這個(gè)演示的源代碼好好研究研究,以進(jìn)行完善汽車組合儀表這個(gè)項(xiàng)目����。圖7 色彩環(huán)漸變效果 圖8 百分比演示效果 圖9 日期設(shè)置效果 圖10 圖表效果 圖11 曲線效果 圖12 信息瀏覽

2017-01-19 11:36:14

例程。(含第三方演示例程)在介紹這兩類例程之前���,先插播一個(gè)小介紹����,就是LPC54608開發(fā)板已有C版本了��,主要區(qū)別由紅色線框標(biāo)出���。說明已有B版本的靈活測(cè)試����,已趨于功能相對(duì)固定。圖1B版本圖2C版本1.

2017-03-24 13:55:37

的使用再進(jìn)行有針對(duì)性的說明�����,此處就從略了�����。圖2 跳接端口 單從開發(fā)板的板載資源來看����,LPC54608還是具備許多功能特色的,并與眾多流行元素相結(jié)合���,主要表現(xiàn)在: 最醒目的當(dāng)屬觸摸屏�����,它可是在中、高檔的開發(fā)板

2017-01-22 09:19:33

的用法還是放到具體的使用再進(jìn)行有針對(duì)性的說明����,此處就從略了。圖2 跳接端口單從開發(fā)板的板載資源來看�����,LPC54608還是具備許多功能特色的,并與眾多流行元素相結(jié)合����,主要表現(xiàn)在: 最醒目的當(dāng)屬觸摸屏,它可

2017-04-12 10:53:43

對(duì)LPC54608開發(fā)板的性能與資源配置有了基本了解后��,我們看一下如何為它構(gòu)建開發(fā)環(huán)境����,以便于進(jìn)行修改流程的驗(yàn)證及應(yīng)用開發(fā)。LPC54608支持多種開發(fā)工具���,但我還是鐘情于使用KEIL���。在正是使用前

2017-01-22 11:58:31

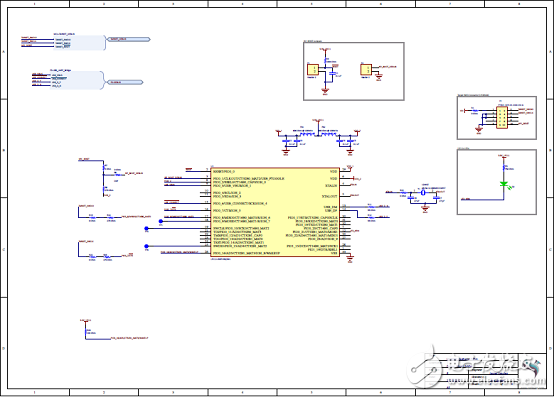

LPC800 開發(fā)板 電路圖.pdf

2016-09-19 08:27:56

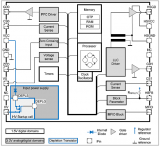

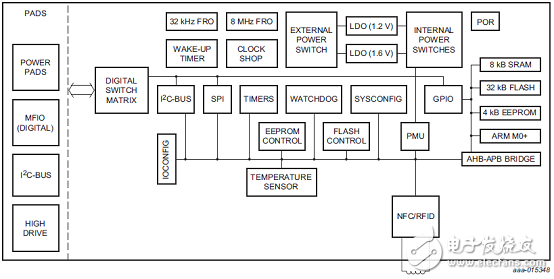

了差異化的產(chǎn)品特性,目前已有 LPC80X�,LPC81X,LPC82X�����,LPC83X�����,LPC84X五個(gè)子系列,以及帶有 NFC 接口的 LPC8N04�����。另外�����,LPC800 系列延續(xù)了所有 LPC 微控制器

2019-09-23 09:05:04

LPC824Lite開發(fā)板怎么樣?

2022-02-11 06:57:33

調(diào)試串口0收發(fā)數(shù)據(jù)��,用調(diào)試助手發(fā)12345678��,但接受到8個(gè)1�����,大神幫忙看一下?�?��!#include "LPC8xx.h"#include #include #define

2018-04-17 10:47:40

N32G030C8L7-STB開發(fā)板硬件使用指南開發(fā)板用于國(guó)民技術(shù)股份有限公司32位N32G030C8L7系列MCU的開發(fā)�。本文檔詳細(xì)描述了N32G030C8L7-STB開發(fā)板硬件使用指南開發(fā)板的功能����、使用說明及注意事項(xiàng)。

2022-11-02 07:57:29

N32G030K8L7_STB開發(fā)板硬件使用指南開發(fā)板用于國(guó)民技術(shù)股份有限公司32位N32G030K8L7系列MCU的開發(fā)��。本文檔詳細(xì)描述了N32G030K8L7_STB開發(fā)板硬件使用指南開發(fā)板的功能���、使用說明及注意事項(xiàng)���。

2022-11-01 07:39:27

N32G031C8L7_STB開發(fā)板用于國(guó)民技術(shù)股份有限公司高性能 32 位 N32G031C8L7 系列芯片的樣片開發(fā)。本文檔詳細(xì)描述了 N32G031C8L7_STB 開發(fā)板的功能���、使用說明及注意事項(xiàng)�。

2022-11-02 07:44:23

N32G032C8L7_STB開發(fā)板用于國(guó)民技術(shù)股份有限公司高性能32位N32G032C8L7系列芯片的樣片開發(fā)�。本文檔詳細(xì)描述了N32G032C8L7_STB開發(fā)板的功能、使用說明及注意事項(xiàng)�。

2022-11-02 07:13:09

N32G032R8L7_STB開發(fā)板硬件使用指南開發(fā)板用于國(guó)民技術(shù)股份有限公司32位N32G032R8L7系列MCU的開發(fā)。本文檔詳細(xì)描述了N32G032R8L7_STB開發(fā)板硬件使用指南開發(fā)板的功能��、使用說明及注意事項(xiàng)�����。

2022-11-01 08:08:44

1 硬件開發(fā)說明1.1 簡(jiǎn)述 N32G430C8L7_STB 開發(fā)板用于國(guó)民技術(shù)股份有限公司 32 位 MCU N32G430C8L7 的開發(fā)。本文檔詳細(xì)描述了 N32G430C8

2022-11-01 08:10:48

lpc2210開發(fā)板電路圖+原理圖[hide][/hide]

2009-09-14 11:07:43

Cortex-A8開發(fā)板原理圖

2015-07-10 21:05:35

`ISU04N65A N溝道 MOSFETISU04N65A N溝道MOSFETTO-251 應(yīng)用范圍特征: ?適配器?符合RoHS標(biāo)準(zhǔn) ?電視主要電源?低導(dǎo)通電阻 ?SMPS電源?低門電荷

2018-09-06 13:45:25

K60N512VMD100 官方開發(fā)板原理圖與PCB�����,附件為cadence格式(.dsn和.brd)���。附件包含BOM

2016-12-09 10:54:48

恩智浦LPC Cortex-M4/M0系列開發(fā)板����,采用LQFP64封裝的LPC54110 MCU,Arduino板型架構(gòu)�,板載調(diào)試器和常用外設(shè)擴(kuò)展,通?���?芍苯永?b class="flag-6" style="color: red">LPC54110開發(fā)板對(duì)MCU性能進(jìn)行評(píng)估和軟件開發(fā)。了解更多>>

2017-06-20 10:33:10

`※概述MYD-LPC1788開發(fā)板是由米爾科技推出的一款基于NXP(恩智浦)LPC1788 Cortex-M3內(nèi)核的全功能開發(fā)板��。該開發(fā)板具豐富的存儲(chǔ)資源��,包括片內(nèi)512 KB FLASH

2014-10-15 10:29:40

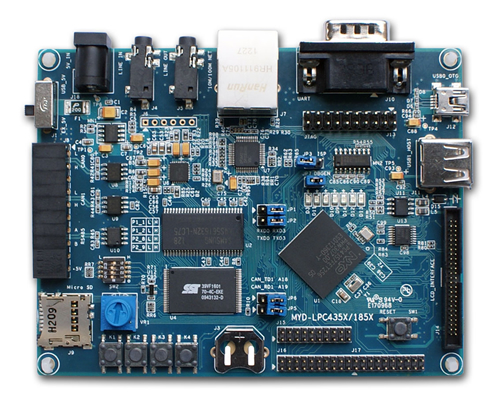

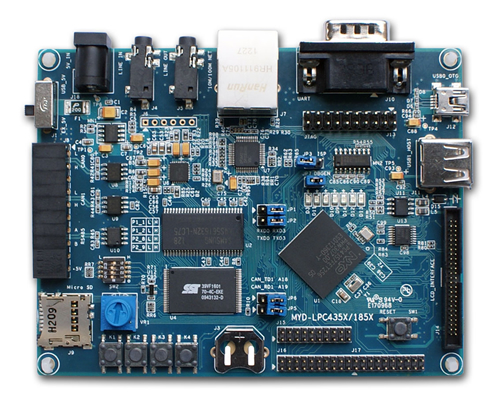

:MYD-LPC1850開發(fā)板(基于NXP公司 LPC1850 芯片)MYD-LPC1857開發(fā)板(基于NXP公司 LPC1857 芯片)圖1 MYD-LPC1850 / LPC1857 開發(fā)板MYD-LPC

2014-10-15 10:24:37

有1788的就好��。查看了官方的ea-lpc1788的電路圖��,用的是串口0�,旺寶的1788開發(fā)板也是用的串口0,按道理說���,編譯后下載到板子串口0會(huì)有信息輸出����。接下來就編譯試試看���。在uboot的頂層目錄

2015-12-09 14:04:19

VK36N8I是什么��?VK36N8I芯片的特性以及應(yīng)用有哪些�?

2021-11-05 07:51:24

開發(fā)板上使用SPI接口實(shí)現(xiàn)TF卡的讀寫����。7,Arduino接口8�����,USB接口 LPC54114這顆芯片只支持全速設(shè)備接口����。不支持USB HOST接口�����,又是一大缺陷����。主要外設(shè)接口就這些���,接下來將一一體驗(yàn)��。

2017-08-07 08:23:48

本帖最后由 辛一_e1e 于 2017-8-15 23:12 編輯

上一章簡(jiǎn)單認(rèn)識(shí)了開發(fā)板的一些特點(diǎn)�����,這一章開始進(jìn)行編程前的準(zhǔn)備——搭建開發(fā)環(huán)境����。這里采用MCUXpresso配置工具進(jìn)行開發(fā)

2017-08-15 23:07:58

NXP LPC54110開發(fā)板開箱萬利公司出品的搭載恩智浦LPC54114系列處理器的開發(fā)板��。先來一波開箱吧�!一、外包裝外包裝一眼看上去還是蠻漂亮的��,而且開發(fā)板主要參數(shù)都寫到了包裝正面����。二�����、套件清單

2017-09-27 22:43:24

有開發(fā)板主要硬件參數(shù)打開包裝盒全部配件如下圖,有LPC54110開發(fā)板�����、排針�、數(shù)據(jù)線、螺絲刀開發(fā)板正面主要元器件分別如下開發(fā)板背面如下圖開發(fā)板PCB如圖開發(fā)板電路原理圖如下開發(fā)板PCB工程圖開發(fā)板

2017-08-05 00:40:53

LPC54110開發(fā)板外包裝如下�����,上面印刷了開發(fā)板的外觀以及功能特性����。拆開包裝可以看到有一塊開發(fā)板,一條micro u***線��,排針和螺絲刀��。開發(fā)板所用的主控LPC54114J256�,為

2017-09-25 23:04:02

下面介紹在NXP LPC54110開發(fā)板上使用數(shù)字計(jì)時(shí)的具體實(shí)現(xiàn)方法�����,我們?cè)诖谳斎霑r(shí)間發(fā)送后����,開發(fā)板就開始一直返回距離我們發(fā)送后時(shí)長(zhǎng)的時(shí)間�,達(dá)到計(jì)時(shí)目的所需輸入的數(shù)字計(jì)時(shí)代碼如下uint8

2017-08-13 00:53:52

].pdf用戶手冊(cè)*附件:UM_N32G031_Series_User_Manual_V2.1_CN[1].pdf勘誤手冊(cè)*附件:ES_N32G031_Series_Errate_Sheet_V1.1_CN[1].pdf開發(fā)板原理圖及PCB*附件:N32G031C8L7-STB_V1.0[1].pdf

2022-11-03 14:37:55

].pdf用戶手冊(cè)*附件:UM_N32G430_Series_User_Manual_V1.1_CN[1].pdf勘誤手冊(cè)*附件:ES_N32G430_Series_Errata_Sheet_V1.1_CN[1].pdf開發(fā)板原理圖及PCB*附件:N32G430C8L7_STB_V1.0[2].pdf

2022-11-03 11:58:44

及設(shè)計(jì)介紹更多精彩內(nèi)容現(xiàn)場(chǎng)大咖演示車內(nèi)體驗(yàn)領(lǐng)域解決方案車用雷達(dá)解決方案基于i.MX 8MQ的人臉識(shí)別更多現(xiàn)場(chǎng)演示好了�����,介紹了那么多�,看視頻挖寶的寶到底有哪些呢?1���、LPC8N04開發(fā)板����,集成了NFC智能

2018-11-21 15:54:08

本帖最后由 z00 于 2016-8-11 09:10 編輯

LPC1768讀寫兩片N25Q256A的原理與實(shí)現(xiàn)

尋址方式:N25Q256是由兩片128Mbit存儲(chǔ)單元疊加而成。支持3字節(jié)地址

2015-04-29 14:24:12

“MiCO 總動(dòng)員”手機(jī) APP控制 MICOKit–LPC5410x開發(fā)板圖5.5 通過“微信公眾號(hào)”控制 MICOKit–LPC5410x開發(fā)板6.方案聯(lián)絡(luò)人 世平集團(tuán) ATU 技術(shù)人員:atu.cn@wpi-group.com``

2015-10-27 08:06:33

關(guān)于LPC54XXX開發(fā)板的知識(shí)點(diǎn)不看肯定后悔

2021-10-26 07:47:18

想問一下怎么用vuv查看pcb設(shè)計(jì)圖���,我看不懂呀�����,怎么辦呀�,求大神幫忙哦

2016-05-10 23:15:36

基于nRF905和LPC2148 ARM開發(fā)板的無線數(shù)據(jù)收發(fā) 如何改為基于nRF905和de2—115開發(fā)板的無線數(shù)據(jù)收發(fā)

2013-12-07 00:16:16

��。我正在使用 LPC8N04 開發(fā)板 OM40002�����。

我立即失去了調(diào)試�,探針根本無法與目標(biāo)對(duì)話����。MCU Expresso 一個(gè)接一個(gè)地給我錯(cuò)誤。

我擔(dān)心我已經(jīng)把開發(fā)板弄臟了���。我該如何取回它��?

8N04 沒有 ISP 引腳...

2023-05-22 07:44:29

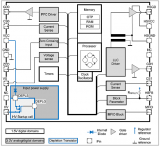

基于LPC8N04]基于LPC8N04 MCU的物聯(lián)網(wǎng)傳感器節(jié)點(diǎn)經(jīng)過獨(dú)特設(shè)計(jì)���,融合了NFC標(biāo)簽功能���,同時(shí)提供了微控制器的功能。這種組合有助于簡(jiǎn)化配置����,允許簡(jiǎn)單的讀/寫功能,并能夠在低成本和低功耗

2018-07-26 10:47:18

怎么實(shí)現(xiàn)HC-SR04+MS5611的四軸飛行器PCB設(shè)計(jì)�?

2021-06-15 07:29:06

我可以得到這個(gè)微控制器的開發(fā)板原理圖和技術(shù)參考手冊(cè)嗎?

零件號(hào):

LPC1778FET208K

2023-05-17 11:37:18

請(qǐng)問我的lpc11c24開發(fā)板接上u***轉(zhuǎn)串口線為什么在電腦看不到com口�����,之前裝了51的u***轉(zhuǎn)串口的驅(qū)動(dòng)�����,這個(gè)開發(fā)板沒有附帶驅(qū)動(dòng)。請(qǐng)問這個(gè)問題怎么解決?���。恐x謝

2013-08-18 00:12:56

用LPC2368開發(fā)板做的USB轉(zhuǎn)ttl線容易出錯(cuò),當(dāng)波特率115200是���,tx和rx連續(xù)發(fā)送時(shí)容易出錯(cuò)��, 是什么原因

2023-11-08 07:33:46

NXP LPC824 + Vishay RGB Sensor 開發(fā)板是世平集團(tuán)推出的一款用于檢測(cè)光的三原色 R(紅)����、G(綠)����、B(藍(lán))數(shù)據(jù)的 EVM���。此開發(fā)板的主控平臺(tái)采用的是 NXP

2019-09-20 09:05:06

是不是都是基于m0+的�����?

2023-11-07 07:29:28

集成NFC技術(shù)LPC8N04 MCU - 概況介紹

2022-12-09 07:02:08

LPC2106 arm開發(fā)板原理圖-電路圖

2009-03-28 09:48:08 156

156 lpc2210開發(fā)板電路圖

2009-09-14 11:07:43 142

142 型號(hào):SUD50N04-8M8P-4GE3-VB絲?����。篤BE1405品牌:VBsemi參數(shù)說明:- MOSFET類型:N溝道- 額定電壓:40V- 最大電流:85A- 導(dǎo)通電阻(RDS

2023-12-14 16:25:40

LPC2138的100M以太網(wǎng)開發(fā)板原理圖

開發(fā)板電路圖

2010-10-19 16:51:35 227

227 LPC213X的10M以太網(wǎng)開發(fā)板原理圖

開發(fā)板電路圖

2010-10-19 16:52:17 225

225 LPC2200開發(fā)板原理圖:

2012-03-20 13:57:47 212

212 lpc1700開發(fā)板_dsp算法庫����,有需要的下來看看。

2016-01-13 17:02:03 6

6 EM-LPC1700開發(fā)板產(chǎn)品說明����,下來看看

2016-06-06 16:03:43 19

19 EM-LPC1700開發(fā)板用戶手冊(cè),下來看看

2016-06-06 16:03:43 11

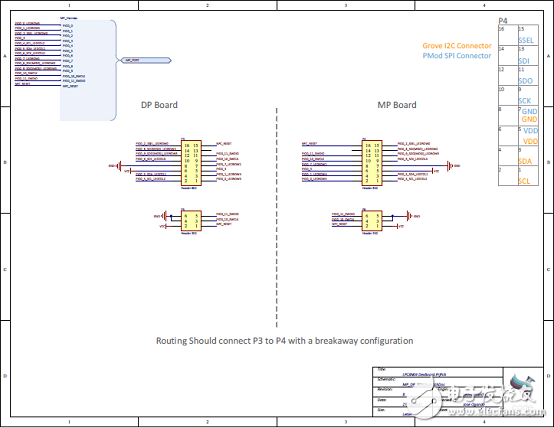

11 基于LPC54102的開發(fā)板電路原理圖

2017-09-08 18:53:06 18

18 本文介紹了IDP2303產(chǎn)品亮點(diǎn)和主要特性,典型應(yīng)用電路圖以及采用IDP2303的120 W 24 V 3.5 A 12 V 3 A SMPS演示板主要特性與指標(biāo),電路圖,材料清單和PCB設(shè)計(jì)圖����。

2018-06-16 15:46:00 18679

18679

通信系統(tǒng)中,通常LPC1768 開發(fā)板可用于應(yīng)用例程中的重要元件����。本文以LPC1768 開發(fā)板為核心,并且分析了其主要的特性��,如高精度�、高速度����、高信噪比�����、良好的實(shí)用性等特點(diǎn)使其成為模/數(shù)轉(zhuǎn)換的極佳

2019-07-16 08:03:00 3808

3808

MYD-LPC185X系列開發(fā)板是深圳市米爾科技有限公司推出的基于NXP(恩智浦)LPC185X系列處理器(Cortex-M3內(nèi)核)開發(fā)板

2019-11-04 14:46:02 3685

3685

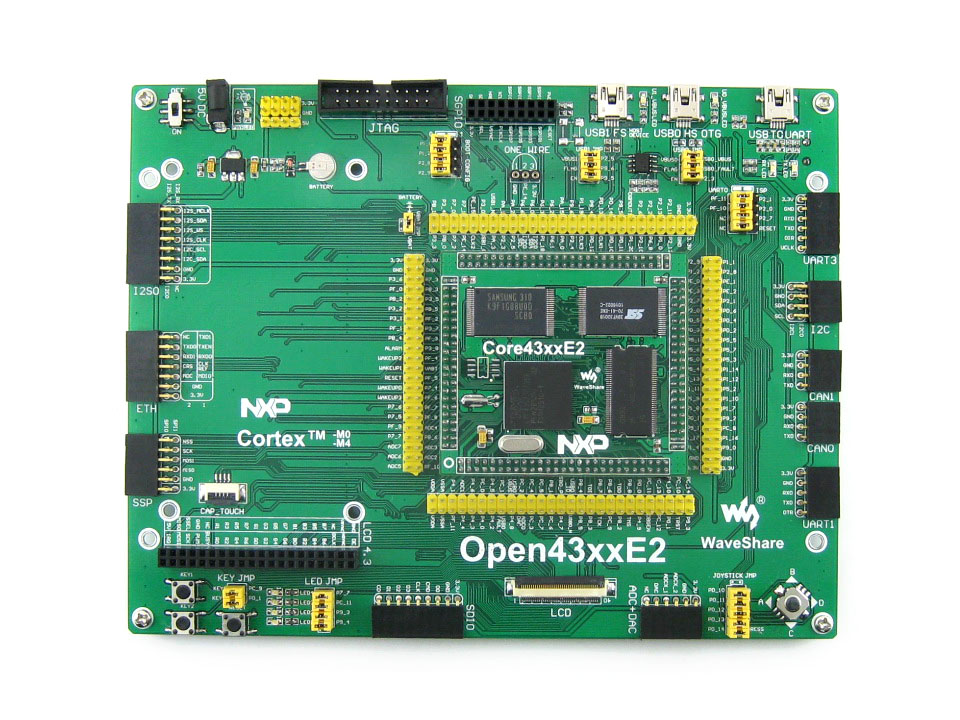

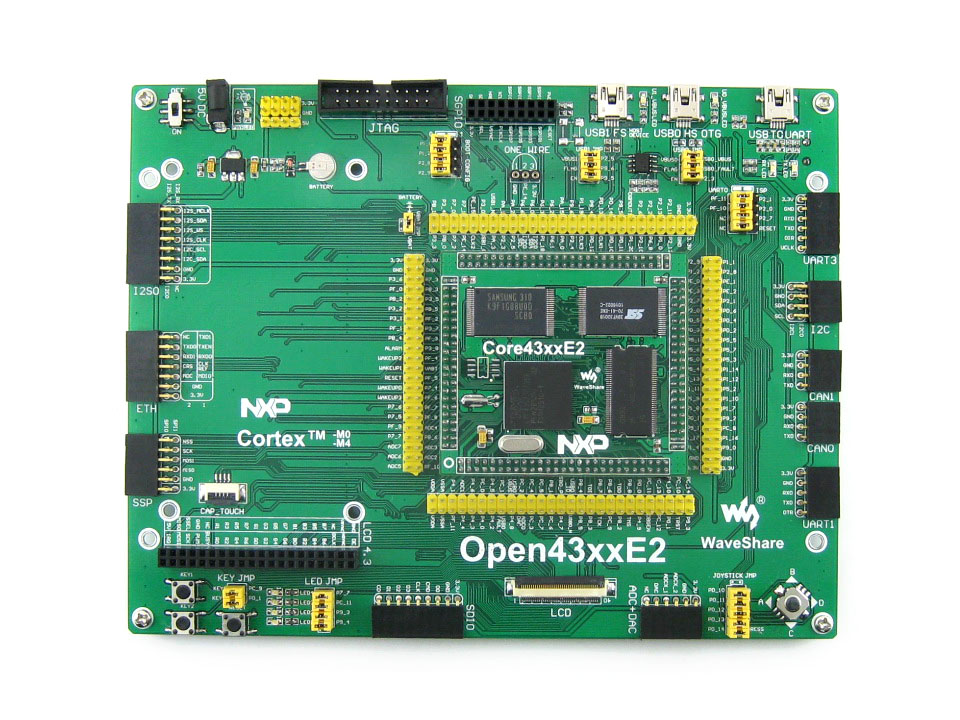

LPC4357開發(fā)板 學(xué)習(xí)板 核心板 標(biāo)準(zhǔn)版本

引出常用接口��,可接微雪外圍模塊

型號(hào) Open4357-C (標(biāo)準(zhǔn)版)

2019-12-29 10:56:38 2441

2441

本文檔的主要內(nèi)容詳細(xì)介紹的是LPC213X系列開發(fā)板圖免費(fèi)下載��。

2020-06-23 08:00:00 4

4 本文檔的主要內(nèi)容詳細(xì)介紹的是LPC1114開發(fā)板的電路原理圖免費(fèi)下載���。

2020-07-20 08:00:00 6

6 ALTIUM DESIGNER原理圖與PCB設(shè)計(jì)資料下載04

2021-10-08 11:19:05 0

0 【嵌入式】LPC54XXX(LPC54608)開發(fā)板資源整合以及簡(jiǎn)單試用

2021-12-04 10:51:04 10

10 LPC845_自制開發(fā)板原理圖�����,已驗(yàn)證

2022-09-26 14:21:30 2

2 2022-11-28 21:04:33 0

0 2022-11-28 21:04:36 0

0 2022-12-05 20:53:14 0

0 2022-12-05 20:53:16 0

0 2022-12-07 23:17:23 8

8 2022-12-07 23:17:24 0

0 2022-12-09 18:49:05 0

0 2022-12-09 18:49:06 0

0 2022-12-12 18:54:36 0

0 2022-12-12 18:54:37 0

0 2022-12-13 07:36:30 0

0 2022-12-13 07:36:31 0

0

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論