用循環(huán)語句設計一個7人投票表決器���,速求

2013-04-23 18:01:49

8人表決器電路,���,源文件

2015-04-12 09:43:57

四人搶答器設計一�����、設計任務及要求:(1)設計用于競賽搶答的四人搶答器����;①有多路搶答�����,搶答臺數(shù)為8;②具有搶答開始后20秒倒計時����,20秒倒計時后無人搶答顯示超時,并報警���;③能顯示超前搶答臺號并顯示犯規(guī)

2012-07-17 10:19:21

三人表決器的VHDL設計實現(xiàn)求代碼

2018-11-10 13:50:50

設計一個七人表決電路:表決結果用不同顏色的LED表示����;表決輸入采用自恢復按鍵,即點動后能夠自動復位的那種��,盡量采用與或非門完成設計���,結果必須最簡����;

2009-05-17 10:10:23

:數(shù)字電路是FPGA的敲門磚���、因為數(shù)字電路主要的內容就是組合和時序��,而組合和時序就是FPGA設計的核心����。HELLO FPGA項目實戰(zhàn)篇:該篇列舉三人表決器��、數(shù)字時鐘��、多功能點歌系統(tǒng)����、數(shù)字示波器這四個實際的工程項目���,手把手帶領大家分析工程���、分解工程、到最終實現(xiàn)工程�����。

2020-05-11 14:31:53

時序電路)。 在組合邏輯電路中�����,任何時刻的輸出僅僅取決于該時刻的輸入���,與電路原來的狀態(tài)無關��。這就是組合邏輯電路在邏輯功能上的共同特點�����。在上一節(jié)中�����,設計的三人表決器就是組合邏輯電路����,輸出與輸入一一對應���,和其他

2023-02-21 15:35:38

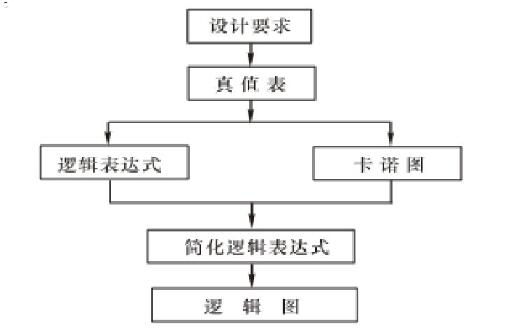

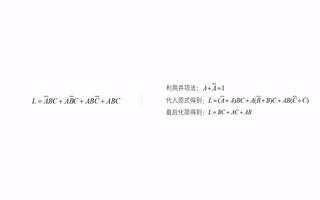

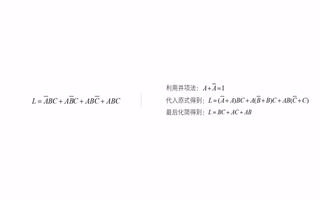

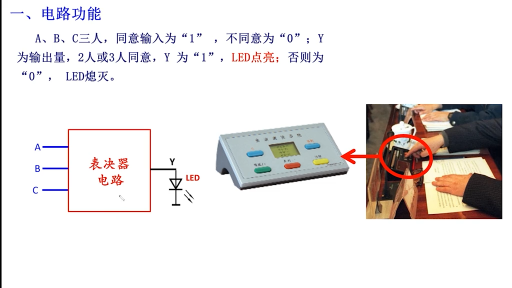

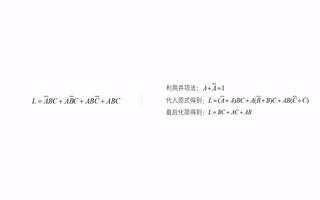

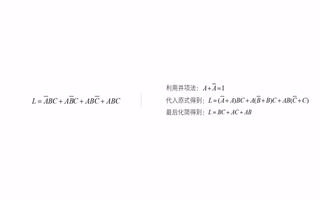

的取值確定之后����,輸出的取值便隨之而定。因此�����,輸出與輸入之間是一種函數(shù)關系��。這種函數(shù)關系稱為邏輯函數(shù)���。 下面利用一個三人表決器的電路設計來說明一些問題���。此電路有三個輸入(A、B����、C)���,一個輸出(Y)��,只有

2023-02-20 17:24:56

ModelSim IntelFPGA中是否提供VHDL源代碼模板����?我注意到該選項存在于標準ModelSim版本中,但我還沒有在IntelFPGA版本中找到它���。以上來自于谷歌翻譯以下為原文

2018-11-14 11:42:38

`項目實戰(zhàn)篇以例舉三人表決器�����、數(shù)字時鐘��、多終端點歌系統(tǒng)��、數(shù)字示波器這四個實際的工程項目���,手把手帶領大家從分析工程、分解工程到最終實現(xiàn)工程��。`

2021-04-06 14:20:59

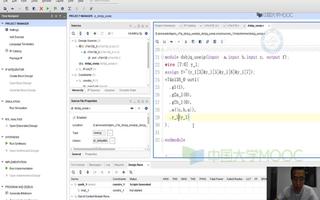

一下RTL圖����,與我們自己手工搭建的要復雜一些。這是由于我們使用的代碼并不是最簡單的��,對于三人表決器門級描述的程序對應到電路圖中應該是比較簡潔的���。了解了程序的基本功能����,分配一下管腳。燒寫到開發(fā)板上���,查看

2016-09-21 22:02:31

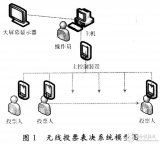

以微型處理器為核心����,外圍配以存儲器�����,鍵盤及l(fā)ed顯示器��,設計出一種實用的無線電子表決器

2019-03-13 15:02:16

現(xiàn)在我在做一個無線表決器��,其他都成功了����,但是就是在報到時無法排除沒有按下報到鍵和沒有上電的表決器�����,我個人認為是表決器返回值時出錯了�����,但我有找不到問題����,希望各位幫幫忙,謝了?��。���。?下面是我集中器發(fā)送

2013-03-14 16:53:57

怎么畫線路圖和原理圖

2018-06-19 12:07:25

本帖最后由 eehome 于 2013-1-5 09:58 編輯

用AT89C51實現(xiàn)三人表決器

2012-08-14 19:39:24

用BD—Ⅳ型��,拼一個三人表決器電路接通開關��,A、B���、C三點:雙向燈綠燈紅燈三點都懸空(不表決)藍滅滅無論哪二點接正�����,另一點接正����、接負�����、懸空滅亮滅無論哪二點接負����,另一點接正、接負����、懸空滅滅亮不使

2019-09-29 20:57:34

你好����,任何人都可以給我一個氣體和煙霧傳感器(MQ5和MQ2)的vhdl源代碼與Spartan-3A套件連接

2019-08-02 10:32:08

超聲波測距模塊源代碼/*************************************參考書目:stm32庫 劉火良編寫人:***模塊功能:超聲波測距使用的資源:定時器 TIM6,PB5

2021-08-19 08:29:50

這兩個警告怎么解決���,一下是源程序,我做的是三人表決��,程序通過���,但是仿真的波形不對啊Warning: No exact pin location assignment(s) for 4 pins

2016-09-28 18:07:55

8051單片機內核VHDL源代碼

This is version 1.1. of the MC8051 IP core.

Jan 31st 2002 - Oregano Systems - Design & Consulting GesmbH

2007-11-12 23:00:18 64

64 正弦波信號發(fā)生器VHDL源代碼

2008-01-02 20:46:30 236

236 SDR SDRAM控制器1?標準SRD SDRAM控制器參考設計���,altera提供 使用手冊 VHDL代碼 Verilog代碼?SDR SDRAM控制器2 標準SRD SDRAM控制器參考設計,xilinx提供 使用手冊 VHDL代碼Verilog

2008-05-20 10:58:59 155

155 不僅具有樹莓派或ANDROID原有的應用外���;我們機器人上位功能同樣源代碼開發(fā)����,同時可通過高配安卓系統(tǒng)加裝的APP軟件進一步發(fā)揮開發(fā)者的想象空間。而且具有高校人工智能機器人專業(yè)教具及實驗

2022-08-07 08:55:14

各種功能的計數(shù)器實例(VHDL源代碼):ENTITY counters IS

?PORT?(??d??: IN ?INTEGER RANGE 0 TO 255;??clk??: IN?BIT;??clear?: I

2009-05-27 08:50:07 58

58 直流步進電機控制器實例(VHDL源代碼):步進電機控制器.vhd,直流電機控制器.vhd

2009-05-27 08:51:54 62

62 漢明糾錯嗎編碼器實例(VHDL源代碼):

2009-05-27 10:11:15 43

43 各種功能的計數(shù)器實例(VHDL源代碼):

2009-05-27 10:19:48 54

54 直流步進電機控制器實例(VHDL源代碼):

2009-05-27 10:23:05 47

47 狀態(tài)機實例(VHDL源代碼):

2009-05-27 10:27:58 59

59

SDRAM控制器參考設計,Lattice提供的VHDL源代碼

-- Permission:

-- Lattice Semiconductor grants

2009-06-14 08:54:28 93

93 UART 4 UART參考設計����,Xilinx提供VHDL代碼 uart_vhdl

This zip file contains the following folders

2009-06-14 08:57:14 113

113 PC機與單片機通信實例:表決器單片機要同時處理很多部分的功能�����,如:按鍵處理���、LED處理�����、通信處理等��。而單片機程序是串行執(zhí)行的���。如何讓眾多任務同時進行或者看起來同時

2009-06-28 00:02:05 70

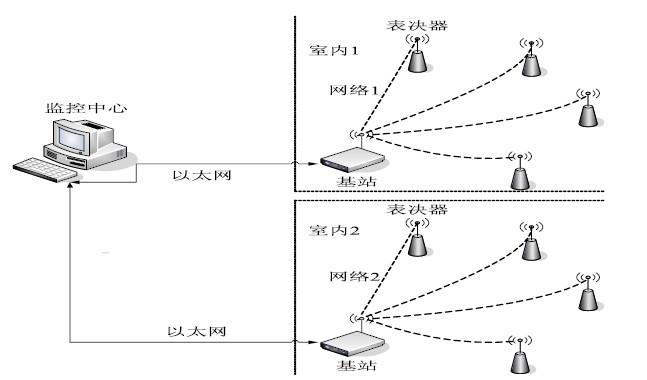

70 介紹了一種基于MSP430F123 和nRF905 的無線表決系統(tǒng)的軟硬件設計與實現(xiàn)。系統(tǒng)通過主控器���、表決器和PC 機實現(xiàn)對表決信息的采集����、處理和顯示。本系統(tǒng)具有低功耗�����、功能強��、可靠性

2009-08-11 08:22:51 51

51 五個ARM處理器核心verilog/VHDL源代碼

有幾中編程語言���。.net.vbh...

2010-02-09 11:32:13 138

138 VHDL源代碼: library ieee;

2010-02-09 15:10:15 43

43 如何看懂源代碼--(分析源代碼方法)

________________________________________我們在寫程式時,有不少時間都是在看別人的代碼����。 例如看小組的代碼,看小組整合的

2010-02-10 14:40:39 51

51 快速編輯源代碼

實驗要求:通過實驗�����,了解網(wǎng)頁源代碼編寫結構機利用Dreamweaver查看網(wǎng)頁自動生成的源代碼��,掌握HTML的常用標記及對網(wǎng)頁中的代碼進行增加和修改���。說

2010-02-10 15:00:18 10

10 登陸系統(tǒng)源代碼

本登陸系統(tǒng)源代碼要供業(yè)余愛好者學習.

2010-02-26 16:22:26 14

14 給用戶提供了FFT的VHDL源代碼下載��,可供用戶來參考學習

2011-03-02 16:43:27 154

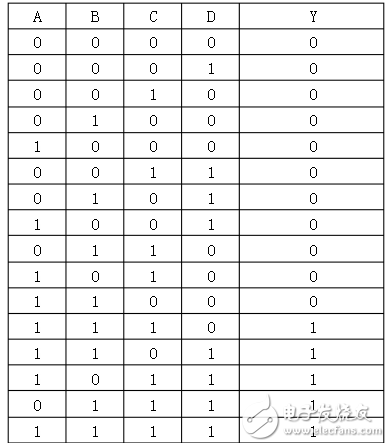

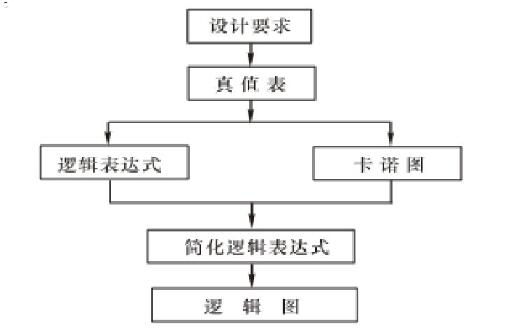

154 我們根據(jù)三人表決器的直值表��,可以通過 卡諾圖 化簡可以得到: L2=SW1SW2 SW1SW3 SW2SW3 L1=_L2 那么我們可以在MAX plusII中用原理圖實現(xiàn)上面的三人表決器 下面僅把和 VHDL 不同的詳細寫下��,相

2012-05-18 15:46:43 8330

8330

打開MAX plusII,在開始菜單內選擇MAX PLUS II 項����,開始運行MAX PLUS II(如下圖) 你最好把圖標放到桌面上,以后直接雙擊MAX PLUS II圖標就可以運行軟件了 在MAX PLUSII上點右鍵����,選擇發(fā)送到-桌面快

2012-05-18 16:37:17 13917

13917

下面僅把和VHDL不同的詳細寫下,相同或基本相同的就一帶而過: (1)打開MAX plusII (2)新建 新建一個verilog-HDL文件(Text Editor File類型) (3)輸入設計文件 其中SW12���,SW13����,SW23為中間變量 module m

2012-05-18 16:37:14 13434

13434

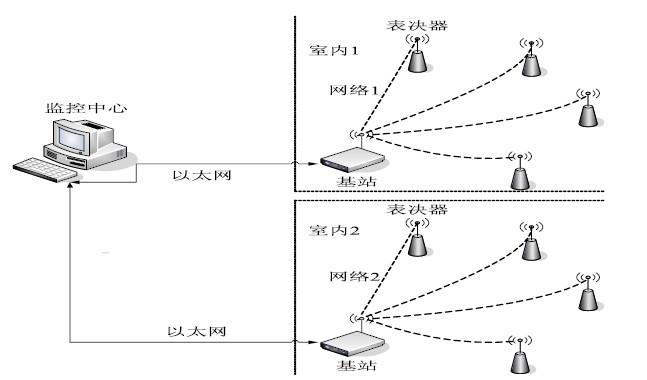

1 引言 投票表決器在選舉,會議��,教學���,娛樂節(jié)目中得到大量的使用?����,F(xiàn)行的無線表決系統(tǒng)采用單一的無線網(wǎng)絡,使無線終端設備與上位機進行通信�����。由于無線網(wǎng)絡存在傳輸距離有限�����,

2012-07-24 16:45:27 1671

1671

本資料是關于基于Quartus II FPGA/CPLD數(shù)字系統(tǒng)設計實例(VHDL源代碼文件)��,需要的可以自己下載����。

2012-11-13 14:03:36 907

907 altera FPGA/CPLD高級篇(VHDL源代碼)

2012-11-13 14:40:38 134

134 掌握在 Quartus Ⅱ開發(fā)環(huán)境下��,運用硬件描述語言輸入法對“三人表決器”進行設計輸入����、編譯����、調試和仿真的方法。

2016-01-15 15:27:33 0

0 VHDL數(shù)字時鐘源代碼�����,工程文件導入Quretus II即可直接運行���。

2016-03-10 15:37:38 41

41 HL配套C實驗例程100例之表決器����,配合開發(fā)板學習效果更好���。

2016-04-11 16:09:41 14

14 Xilinx FPGA工程例子源碼:用FPGA模擬VGA時序PS_2總線的鍵盤接口VHDL源代碼

2016-06-07 15:11:20 32

32 以前寫論文收集的一些資料���,學習單片機、C語言的好資料?���。�����。����?�!

2016-07-08 13:58:47 4

4 基礎的電子類資料��,設計和開發(fā)必備資料���,快來下載學習吧。

2016-09-28 11:57:32 12

12 VHDL例程代碼����,感興趣的小伙伴們可以瞧一瞧。

2016-11-11 18:10:18 2

2 vhdl基礎實例源代碼��,感興趣的小伙伴們可以瞧一瞧����。

2016-11-11 17:17:12 5

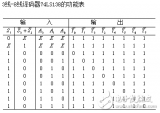

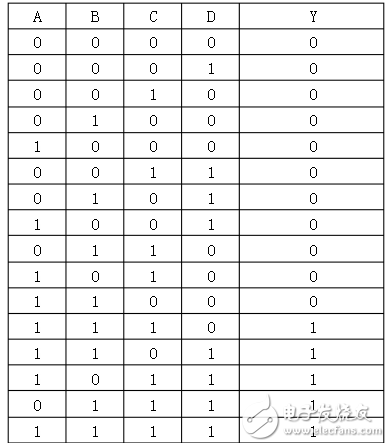

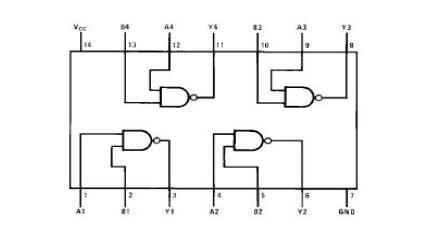

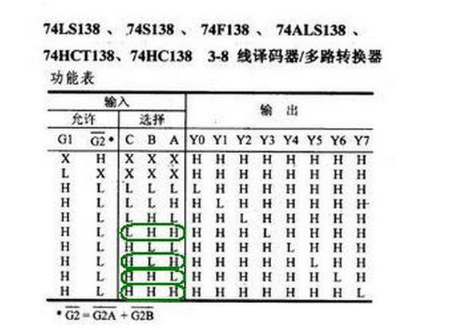

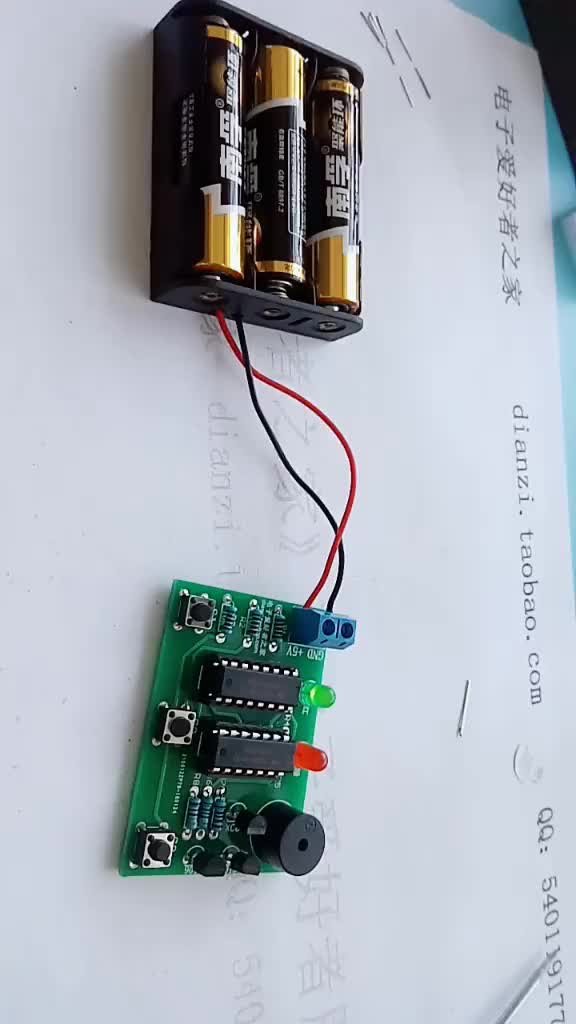

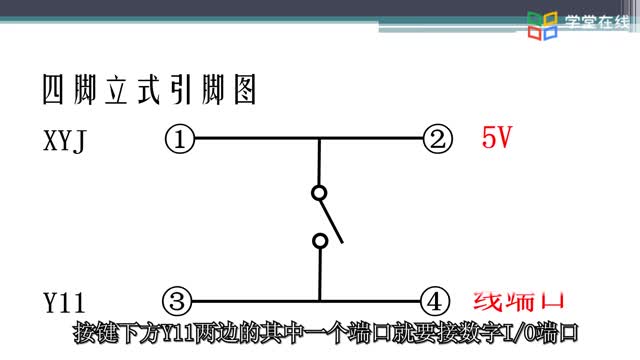

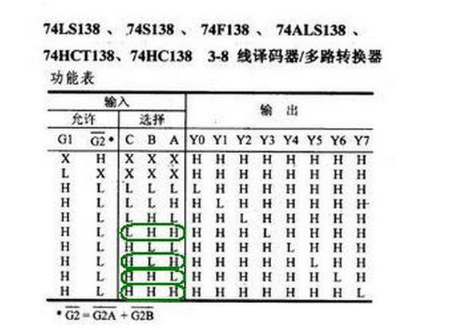

5 三人表決器主要由一個3-8位譯碼器(74LS138)和2個4輸入與非門(74LS20)組成���。通過三個按鈕接受用戶輸入。按鈕按下表示同意���,不按下表是否決����,當沒有人按下按鈕時���,或只有一個人按下按鈕

2017-10-31 15:13:25 92965

92965

VHDL作為電路的硬件描述語言����,并且已經(jīng)在電路中得到了廣泛的運用���。本文主要介紹了什么是vhdl����、vhdl有哪些特點���、vhdl的優(yōu)勢以及詳細的說明了8位移位寄存器vhdl代碼詳情�����。

2017-12-22 15:11:01 16224

16224 本文為大家?guī)砦宸N三人表決器電路設計方案��,包括兩款仿真電路及程序分析��,三款邏輯電路設計的原理詳解����。

2018-01-17 18:49:21 298033

298033

本文為大家分享四款四人表決器電路設計的原理及方案詳細。

2018-01-17 19:13:09 142800

142800

本文為大家?guī)砦蹇钗迦?b class="flag-6" style="color: red">表決器電路設計方案�����。

2018-01-18 09:18:07 98683

98683

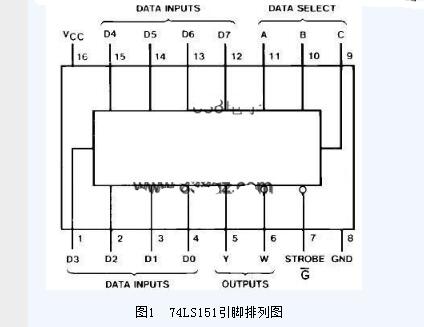

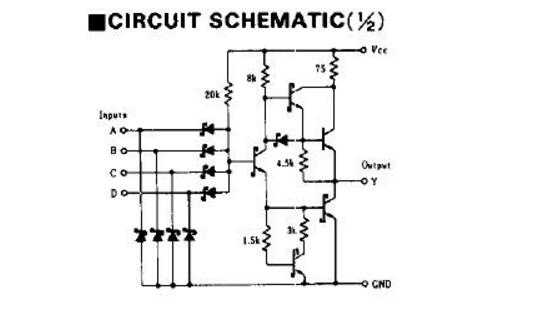

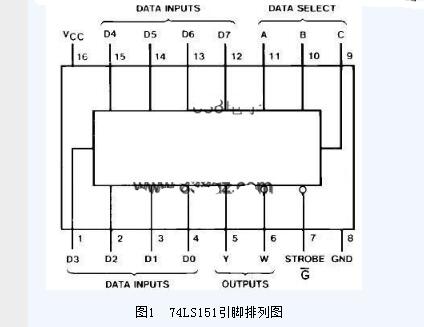

本文介紹了4種方式實現(xiàn)三人表決電路�����。其中包括用74LS00���,74LS20實現(xiàn)三人表決電路、用譯碼器138和與非門74LS20設計實現(xiàn)三人表決電路����、用8選1數(shù)據(jù)選擇器74LS151實現(xiàn)三人表決電路以及用4選1數(shù)據(jù)選擇器74LS153實現(xiàn)三人表決電路方法。

2018-01-26 17:26:20 335165

335165

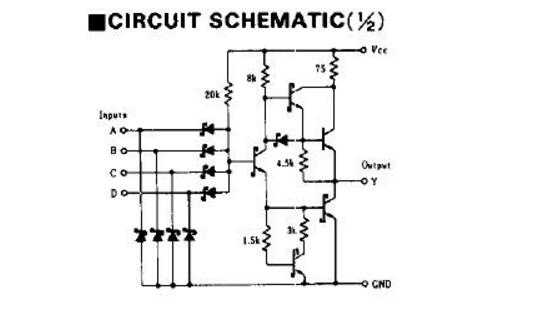

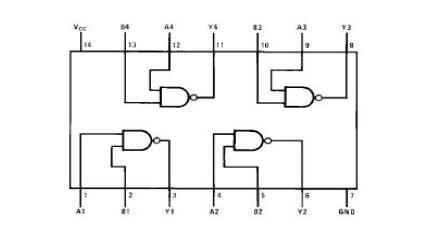

本文開始介紹了74LS00管腳排列圖與74ls00的功能表,其次介紹了74ls00應用電路與74ls00的極限值��,最后介紹了74ls00制作三人表決器邏輯電路的設計步驟與調試��。

2018-02-08 15:42:56 243528

243528

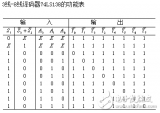

本文開始介紹了74LS20功能表與74LS20引腳圖��,其次介紹了74LS20真值表����,最后詳細介紹了74ls20實現(xiàn)的四人表決器電路并對工作原理、電路仿真及調試進行了相應的介紹��。

2018-02-08 16:18:08 90713

90713

74ls151是常用的8選1數(shù)據(jù)選擇器��。本文主要介紹了74ls151引腳圖��、74ls151邏輯圖及74ls151真值表��,詳細的闡述了74ls151實現(xiàn)三人表決器電路����。

2018-02-08 16:59:36 177218

177218

本文主要介紹了五款74ls138的應用電路圖。其中包括了74ls138全加器電路��、74ls138搶答器電路����、74ls138實現(xiàn)邏輯函數(shù)�����、74ls138全減器電路以及與74LS20組合的三人表決器電路���。

2018-05-04 10:31:55 95858

95858

本文主要介紹了74ls151應用電路圖大全(全加器\表決器)。五人表決器�����,只要贊成人數(shù)大于或等于三����,則表決通過。因此����,只需將每位表決人的結果相加,判斷結果值�����。設五個開關A����、B、C����、D、E作為表決器

2018-05-07 11:38:47 108521

108521

在三人表決器的設計中�����,如果數(shù)字系統(tǒng)簡單�����,可以采用門電路����;如果數(shù)字系統(tǒng)復雜,則可以采用譯碼器��、數(shù)據(jù)選擇器和加法器比較好�����。

2018-08-07 09:31:14 161411

161411

投票表決器在選舉��,會議,教學����,娛樂節(jié)目中得到大量的使用。現(xiàn)行的無線表決系統(tǒng)采用單一的無線網(wǎng)絡��,使無線終端設備與上位機進行通信���。由于無線網(wǎng)絡存在傳輸距離有限����,對障礙物穿透性較差等問題����,無法實現(xiàn)遠程監(jiān)控

2018-12-26 09:10:00 4425

4425

該設計實現(xiàn)了基于MSP430F135和CCllOO的無線表決系統(tǒng)的主控制裝置和表決器的軟硬件,并利用Microsoft Visual Studio 2005實現(xiàn)了系統(tǒng)PC機軟件的設計�����,同時用非接觸式射頻卡儲存?zhèn)€人信息�����,省時省力�����,在平時民主測評中以及其他相應場合的應用前景非常廣泛。

2018-09-13 09:32:00 5404

5404

多數(shù)表決器常見于信號處理���。例如,在自動控制中�����,對三個針對同一事物的信號使用多數(shù)表決器進行運算���,并按照其中兩個一致的結果執(zhí)行�����。這樣既可以提高信號的可靠性(信號不止一個)�����,又避免信號源錯誤(出錯的信號在表決中被排除)造成不必要的損失��。

2019-12-04 07:02:00 2675

2675

表決器���,是投票系統(tǒng)中的客戶端��,是一種代表投票或舉手表決的表決裝置��。表決時����,與會的有關人員只要按動各自表決器上“贊成”��、“反對”��、“棄權”的某一按鈕����,熒光屏上即顯示出表決結果。目前����,表決器可分為有線

2019-09-23 07:09:00 2043

2043

表決器,是投票系統(tǒng)中的客戶端�����,是一種代表投票或舉手表決的表決裝置��。表決時�����,與會的有關人員只要按動各自表決器上“贊成”、“反對”���、“棄權”的某一按鈕����,熒光屏上即顯示出表決結果�����。

2019-09-23 07:05:00 2725

2725

我們例舉三人表決器�����、數(shù)字時鐘����、多終端點歌系統(tǒng)�����、數(shù)字示波器這四個實際的工程項目����,手把手帶領大家從分析工程����、分解工程�����、到最終實現(xiàn)工程����。通過逐個解決工程中的實際問題,來學習原汁原味的FPGA設計�����。本篇一改

2019-12-06 07:05:00 6384

6384

本文檔的主要內容詳細介紹的是VHDL語言設計的全加器源代碼和工程文件免費下載�����。

2019-06-03 08:00:00 4

4 本文檔的主要內容詳細介紹的是使用VHDL設計的數(shù)碼管掃描源代碼免費下載�����。

2019-10-28 11:50:52 2

2 本文檔的主要內容詳細介紹的是組合邏輯電路三人表決器的設計資料詳細說明。

2019-12-03 08:00:00 12

12 本文檔的主要內容詳細介紹的是使用單片機實現(xiàn)七人表決器的程序和仿真資料免費下載�����。

2020-06-22 08:00:00 30

30 本文檔的主要內容詳細介紹的是8人表決器的電路圖免費下載����。

2020-06-28 16:46:00 49

49 本文檔的主要內容詳細介紹的是脈寬測量電路的VHDL源代碼免費下載。

2020-08-04 17:02:56 3

3 本文檔的主要內容詳細介紹的是27個FPGA實例源代碼合集包括了:頻率計程序設計與仿真����,LED控制VHDL程序與仿真,LED控制VHDL程序與仿真���,基帶碼發(fā)生器程序設計與仿真,出租車計價器VHDL程序與仿真��,步進電機定位控制系統(tǒng)VHDL程序與仿真等等

2021-01-14 16:26:48 66

66 關于Actel 的FPGA的譯碼器的VHDL源代碼(通信電源技術期刊2020年第14期)-關于Actel 的FPGA的譯碼器的VHDL源代碼����。適合感興趣的學習者學習,可以提高自己的能力�����,大家可以多交流哈

2021-09-16 15:18:01 10

10 基于VHDL語言中數(shù)字鐘的整點報時源代碼下載

2021-12-15 14:52:56 2

2 protel dxp 三人表決器

2022-06-14 15:00:26 0

0 基于51單片機的表決器例程源代碼例程源代碼

2023-05-12 15:55:13 1

1 基于51單片機的表決器例程源代碼例程源代碼

2023-05-18 09:54:43 0

0 [源代碼]Python算法詳解[源代碼]Python算法詳解

2023-06-06 17:50:17 0

0

電子發(fā)燒友App

電子發(fā)燒友App

評論