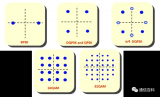

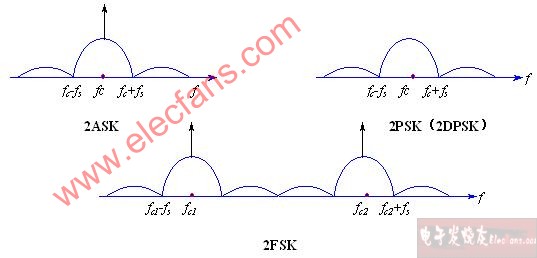

在模擬調制中���,載波參量的改變是按連續(xù)的模擬信息���。在數(shù)字調制中,這些載波參數(shù)(幅度���,頻率和相位)的變化由離散的數(shù)字信號決定���。從這個意義上講,數(shù)字調制和模擬調制并無本質區(qū)別���。數(shù)字調制信號只須表示離散

2023-11-15 10:17:21 631

631

:a.發(fā)射機���,b.接收機上圖給出了單向通信鏈路的簡化框圖。在發(fā)射機端���,一信息信號被調制并與本機振蕩器(LO)混頻���,上變頻到載波頻率���。帶通濾波器(BPF)用于混頻器的前、后以阻斷不需要的諧頻���。先把信號

2017-12-22 16:33:46

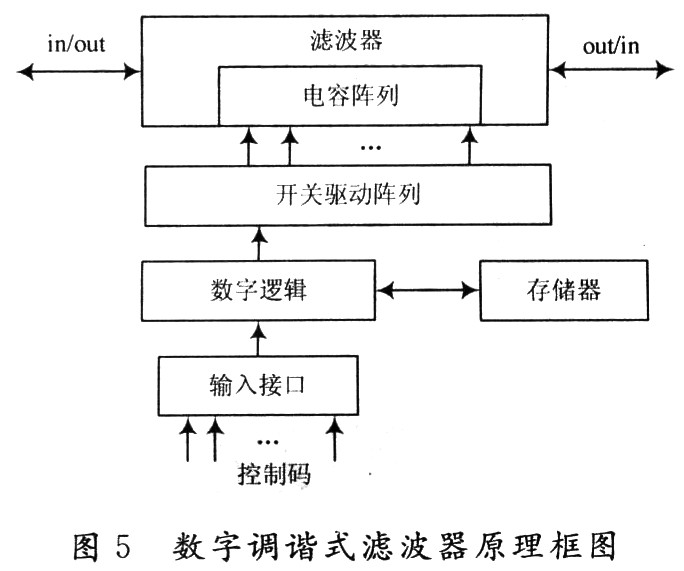

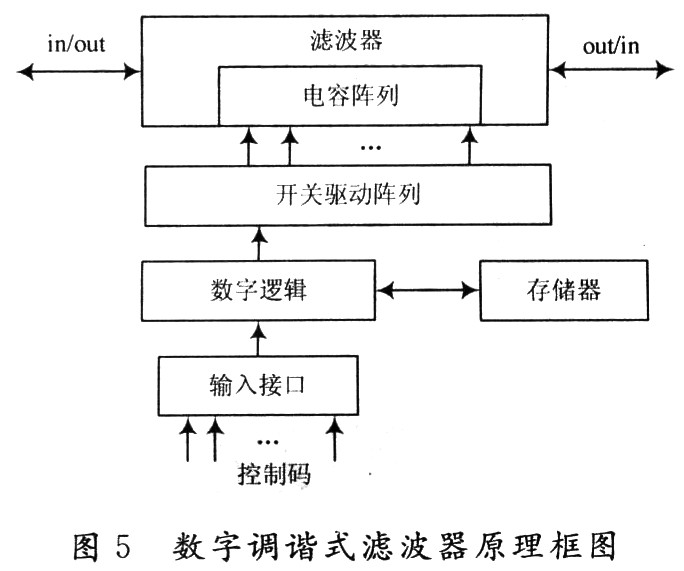

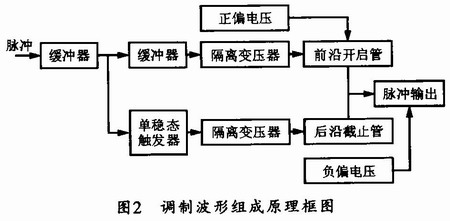

需要傳送的數(shù)字或模擬信號信息一般是低頻信號,必須被載波調制到特定射頻段才能通過天線發(fā)射出去���。隨著通訊技術發(fā)展���,定載頻技術在軍事通訊中的保密、抗干擾���、頻帶利用等方面逐漸暴露出問題���,為解決這些問題,跳頻

2019-08-19 07:10:57

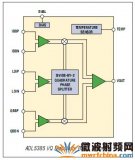

信號���,然后分別經(jīng)過DAC 變換為模擬I 和Q 信號���,最后經(jīng)過IQ 調制器完成上變頻���,圖1給出了數(shù)字調制的簡要架構示意圖。作為整個數(shù)字調制發(fā)射系統(tǒng)的關鍵部件���,IQ 調制器完成了基帶信號的頻譜搬移,從而

2020-07-01 11:15:21

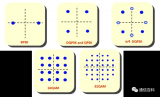

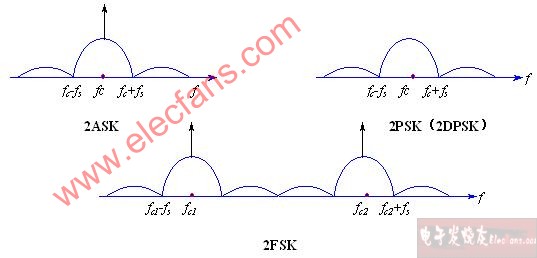

數(shù)字調制系統(tǒng)6.1 引言6.2 二進制數(shù)字調制原理6.3 二進制數(shù)字調制系統(tǒng)的抗噪聲性能6.4 多進制數(shù)字調制系統(tǒng)數(shù)字調制也稱鍵控信號,有三種基本的調制方式:ASK����,F(xiàn)SK,PSK可看成是模擬

2008-10-23 11:28:49

是否有AN描述如何測量數(shù)字調制載波的(Co + No)/ No����?使用什么RW是否重要? CW C / N測量中使用的校正因子是否適用����? 以上來自于谷歌翻譯 以下為原文

2019-01-29 06:51:22

BGTV4152型全固態(tài)電視發(fā)射機的原理是什么����?怎么維護BGTV4152型全固態(tài)電視發(fā)射機?

2021-06-03 06:06:32

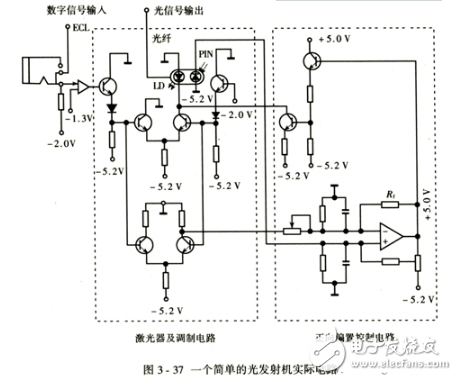

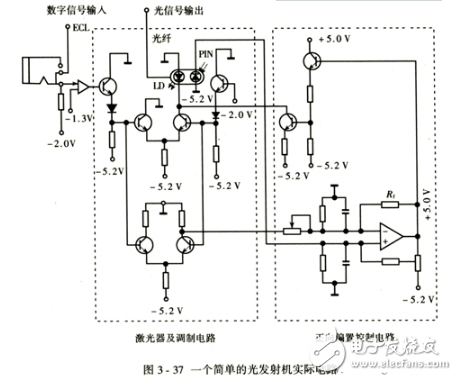

ECL電源開關在數(shù)字光發(fā)射機中的應用是什么����?

2021-05-27 07:16:46

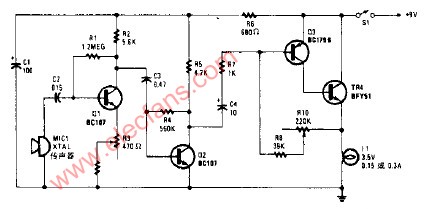

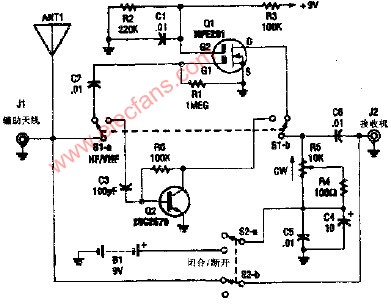

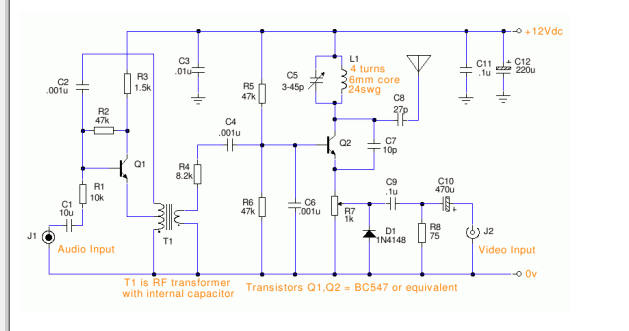

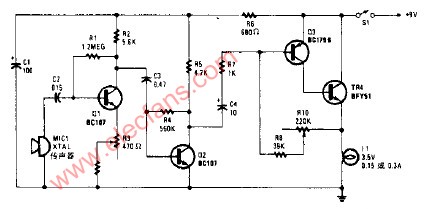

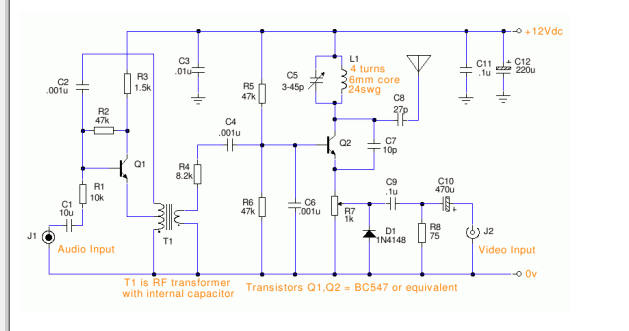

自制簡易FM發(fā)射機

2013-11-11 13:52:22

誰有基于FPGA的2PSK數(shù)字調制解調Verilog代碼����,有的發(fā)份我學習下,謝啦����!QQ:975406162

2013-07-23 19:38:45

現(xiàn)代數(shù)字無線通信發(fā)射機的設計給設備設計者們帶來了越來越多的挑戰(zhàn)。數(shù)據(jù)吞吐量不斷增長的趨勢����,使得所發(fā)射信號的調制密度和載波帶寬也隨之增加。在傳送相同有效值(rms)功率電平的信號時����,要保持良好的相鄰

2019-07-04 06:59:37

、寬帶噪聲以及總雜散噪聲����。混頻器性能與驅動它的本振性能一樣����,因此高質量的本振是提高發(fā)射機總體性能的關鍵����。此外����,本振信號上很小的相位噪聲或雜散分量都有可能在模擬信號路徑中引入足夠大的能量,導致發(fā)射機不能

2018-08-21 09:21:18

出廠時需要對功率放大器的輸出功率進行某種形式的校準����。根據(jù)復雜度和有效性����,存在著多種校準算法。本文將集中討論如何實現(xiàn)典型的RF功率控制方案����,并且將比較多種出廠校準算法的效果和效率。集成功率控制的典型無線發(fā)射機

2019-06-25 07:46:11

本文討論了移動通信向第三代(3G)標準的演化與發(fā)展,給出了范圍廣泛的3G發(fā)射機關鍵技術與規(guī)范要求的概述����。文章提供了頻分復用(FDD)寬帶碼分多址(WCDMA)系統(tǒng)發(fā)射機的設計和測得的性能數(shù)據(jù)����,以Maxim現(xiàn)有的發(fā)射機IC進行展示和說明����。

2021-06-02 06:47:56

和中小功率短波通信發(fā)射機一樣, 經(jīng)歷了電子管晶體管����、窄帶一寬帶、人工調諧―自動調諧����、模擬-數(shù) 字化、手動控制T自動控制的變化����,每一次新技術的應用,都帶來性能 和功能上的提高����。目前,在國內使用較多

2021-12-16 10:24:19

調頻發(fā)射機作為一種簡單的通信工具����,由于它不需要中轉站和地面交換機站支持����,就可以進行有效的移動通信����,因此深受人們的歡迎。目前它廣泛的用于生產(chǎn)����、保安、野外工極管完成語音信號對載波信號的頻率調制����,并通過

2012-05-20 10:51:34

【正文快照】:1引言近年來,由于半導體技術和數(shù)字技術的飛速發(fā)展,西方等發(fā)達國家,先后研究出大功率的高頻半導體器件,將大功率的固態(tài)器件采用數(shù)字技術應用于廣播發(fā)射機領域,形成幾種新的制式,如,固態(tài)PDM

2010-04-23 11:29:25

什么是數(shù)字調制?如何去進行數(shù)字調制����?有哪些步驟流程?

2021-06-21 06:42:57

本應用指南介紹了影響 CCDF 功率曲線的主要因素����,以及 CCDF 曲線如何幫助您進行系統(tǒng)和元器件設計����。 本應用指南中使用了 Keysight E4406A VSA 系列發(fā)射機測試儀����。

2019-03-27 06:53:02

借助多功能 Keysight ESG-D 系列射頻信號發(fā)生器,用戶能夠與數(shù)字通信標準的變化保持同步����。 Keysight ESG-D 系列射頻信號發(fā)生器提供了兩種具有補充特性的基帶體系結構,可生成復雜的數(shù)字調制信號����。

2019-05-30 06:28:06

模擬光發(fā)射機按光波長分為兩大類: 1310nm 光發(fā)和 1550nm 光發(fā)。由于 1310nm 光發(fā)是把射頻電視信號直接加在激光二極管上進行光強度調制的����,稱為內調制光發(fā): 1550nm 波長光發(fā)是把

2019-10-18 06:35:10

度增大,使CTB、cs0非線性指標劣化����,還會造成DFB激光器的過驅動,導致光發(fā)射機輸出功率下降����;輸入電平過小,光調制度降低����,則導致光發(fā)射機的載噪比指標不能滿足需求?���! ?.光纖連接器與法蘭盤均屬精密器件

2022-04-16 22:06:17

的是一個只有3個集成部件的發(fā)射機無線電解決方案。以上就是ADI提供的新的完整的系統(tǒng)解決方案����。完整解決方案專場

2018-08-01 09:49:01

如題����,直接上變頻發(fā)射機中����,采用Passive Mixer的話����,PA輸出會有flo+3*fbb的spur����,不但造成ACP變差,嚴重時還會影響發(fā)射機的EVM����。請問站內大神們,這個問題有什么好的解決方法呢����?

2021-06-23 09:58:10

的調相信號,可避免由功放的非線性所帶來的不利影響����,因而既保證了發(fā)射機的高線性度,又保證了發(fā)射機的高效率����。理論上功放的效率可以達到100%,這對于非恒包絡調制技術有著極其重要的意義����。其中輸入信號分離成兩路恒

2019-06-17 07:41:26

求神人幫我解決基于Labview的數(shù)字通信系統(tǒng)發(fā)射機的設計����,其中包括模擬信源數(shù)字化編碼����,數(shù)字信號基帶傳輸,數(shù)字調制傳輸����,正交調制電路等模塊。

2014-05-10 10:27:31

基于Labview的數(shù)字調制解調設計 內有文章和程序 發(fā)現(xiàn)網(wǎng)上很少有這發(fā)面的資料 故而發(fā)此文章

2012-05-17 19:37:08

本文基于VHDL方式實現(xiàn)了QPSK數(shù)字調制解調電路的設計����,通過QuartusII軟件建模對程序進行仿真,并通過引腳鎖定����,下載到FPGA芯片EP1K30TC144—3中,軟件仿真和硬件驗證結果表明了該

2020-12-18 06:03:26

`大功率發(fā)射機的水冷散熱解決方案調頻廣播發(fā)射機主要用于將調頻廣播電臺的語音和音樂節(jié)目以無線方式發(fā)射出去����。而傳調頻廣播發(fā)射機在運行的過程中會產(chǎn)生一定的熱量,溫度對發(fā)射機的性能影響比較大����,溫度過高或過低

2018-11-28 15:47:02

于實現(xiàn)自適應處理等特點����,給數(shù)字信號處理帶來了巨大的發(fā)展機遇?���;谏鲜鰞?yōu)點,那么我們可以利用DSP設計軟件無線電基頻發(fā)射機嗎����?

2019-08-02 08:25:09

文末下載完整資料簡易無線電遙控系統(tǒng)[2](第二屆,1995年)(1)設計任務??設計并制作無線電遙控發(fā)射機和接收機����。無線電遙控發(fā)射機方框圖如圖1.3.9所示。無線電遙控接收機方框圖如圖1.3.10

2022-01-25 07:31:58

; 一����。前言: 在這里我將要向大家介紹一種簡單易制的小型調頻發(fā)射機。它不但滿足了發(fā)射距離的要求����,而且還能同時用話筒和線路輸入聲音信號����,進行背景配音����。電路還加入了調制

2008-11-02 14:36:50

怎么實現(xiàn)乒乓球發(fā)射機的設計����?

2021-11-09 06:56:09

手持發(fā)射機遙控LED系統(tǒng)硬件主要有哪幾部分����?手持發(fā)射機遙控LED系統(tǒng)軟件是由哪些模塊組成的?如何對手持發(fā)射機遙控LED系統(tǒng)的性能進行測試����?

2021-06-08 06:00:37

該多功能無線護理求助裝置由發(fā)射機和接收機組成。發(fā)射機設計有無線傳遞吃飯����、喝水、吃藥����、解手四種求助信息的功能����;接收機對應有四種求助信息的接收功能����。

2021-05-06 12:56:38

大家好����,請問大家有沒有用過單片機實現(xiàn)2FSK數(shù)字調制解調器呢?有的話吱一聲……謝謝����!

2013-09-11 23:35:35

求一種手持發(fā)射機遙控LED廣告牌的設計方案

2021-05-25 06:12:15

本人菜鳥 望論壇大神幫解決一下單片機的問題基于S51 調幅發(fā)射機的設計載波頻率 f=12MHz調制信號:1kHz正弦波穩(wěn)定度 《=10的-4調幅系數(shù) 0.5輸出功率Pa》=30mW天線形式 拉桿天線

2014-07-01 20:05:50

這是一個小型電視發(fā)射機電路����,具有VHF,負聲音調制和PAL視頻調制����。它適用于使用B和G系統(tǒng)的國家����。

簡單的電視發(fā)射機電路圖

2023-08-01 17:00:46

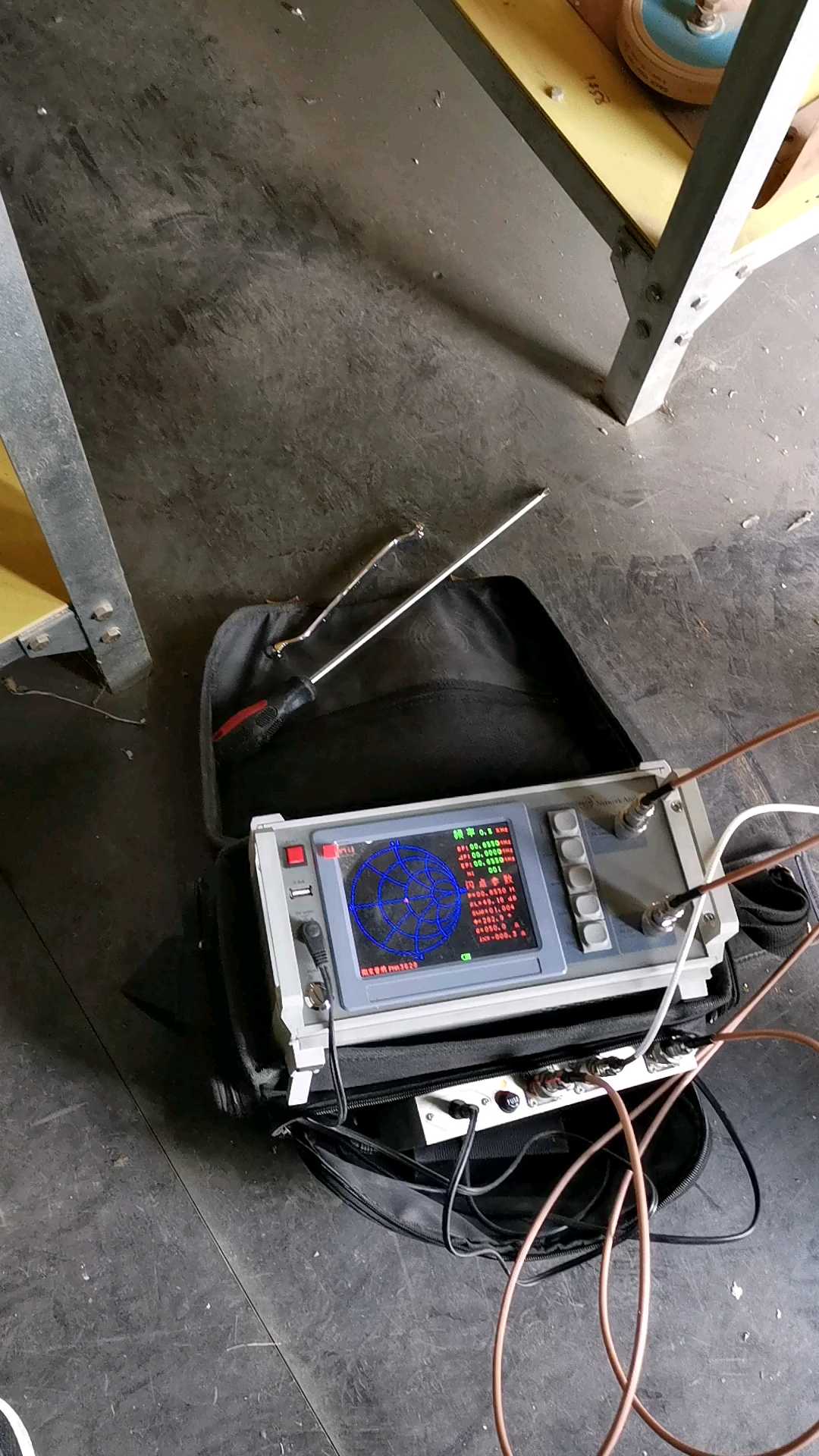

雷達發(fā)射機是由哪幾部分組成的����?怎么提高雷達發(fā)射機的探測距離?雷達發(fā)射機的峰值功率和平均功率有什么關系����?

2021-06-26 07:08:34

。支持所有的通用數(shù)字和模擬電視 標準����,以及大部分音頻廣播標準。 SFE100測試發(fā)射機主要特點 實時編碼單制式信號發(fā)生器 SFE100測試發(fā)射機支持所有的通用數(shù)字和模擬電視標準 100kHz

2019-12-25 15:05:33

寬帶直接變頻發(fā)射機電路功能與優(yōu)勢是什么?請問如何設計并模擬寬帶直接變頻發(fā)射機����?

2021-04-13 06:32:29

誰有基于FPGA的數(shù)字調制器的程序啊,急用啊ASK,PSK,.FSK,QPSK等

2014-04-14 22:31:30

通帶數(shù)字調制解調-通信原理仿真實驗

2009-10-11 09:04:55

是為雷達系統(tǒng)提供一種滿足特定要求的大功率發(fā)射信號����,經(jīng)過饋線和收發(fā)開關由輻射到空間����。雷達發(fā)射機通常分為脈沖調制發(fā)射機和連續(xù)波發(fā)射機����。其中脈沖調制雷達發(fā)射機又分為單級振蕩式發(fā)射機和主振放大式發(fā)射

2021-09-17 09:10:02

本篇博文是看完西安電子科技大學的魏青老師的課程所做的學習筆記,特此記錄����。文章目錄雷達發(fā)射機的任務和基本組成雷達發(fā)射機的主要質量指標脈沖調制器雷達發(fā)射機的任務和基本組成雷達發(fā)射機的任務任務:產(chǎn)生大功率

2021-09-14 08:08:56

第 6 章 正弦載波數(shù)字調制系統(tǒng)§ 6.1 引言 § 6.2 二進制數(shù)字調制原理 § 6.3 二進制數(shù)字調制系統(tǒng)抗噪聲性能 § 6.4 二進制數(shù)字調制系統(tǒng)的性能比較

2008-09-05 00:08:18 45

45 本文提出了一種QPSK 高性能數(shù)字調制器的FPGA 實現(xiàn)方案����,由Altera 的IP 核NCO2.3.0 提供QPSK高穩(wěn)定度的數(shù)字正弦信號,給出了QPSK 的實驗仿真結果����。結果表明,基于NCO 的QPSK 數(shù)字調制器極大

2009-09-26 08:56:55 43

43 本文通過對寬帶數(shù)據(jù)鏈及其關鍵技術的研究����,提出了一種基于 DSP 的數(shù)字調幅廣播DRM(Digital Radio Mondiale)編碼調制器的實現(xiàn)方案,給出了編碼調制器的功能結構描述����、硬件實現(xiàn)方案

2009-12-28 11:23:54 20

20 FPGA在軟件無線電中的工程應用之數(shù)字調制解調篇

2010-02-09 11:14:48 60

60 目 錄摘要4簡介4無線應用與數(shù)字調制5-12無線發(fā)射面臨的挑戰(zhàn)5為什么要數(shù)字調制����?6什么是數(shù)字調制����?7數(shù)字調制應用12數(shù)字無線測試12-19發(fā)射機-I-Q調制器測

2010-06-30 17:19:15 16

16 實驗 數(shù)字調制

一、 實驗目的

1����、掌握絕對碼、相對碼概念及它們之間的變換關系����。

2009-04-01 08:51:38 7270

7270

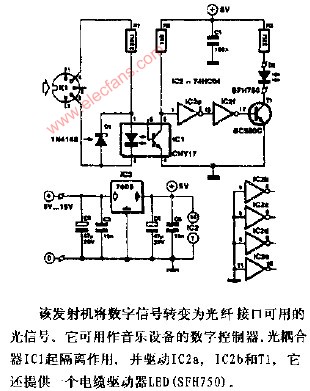

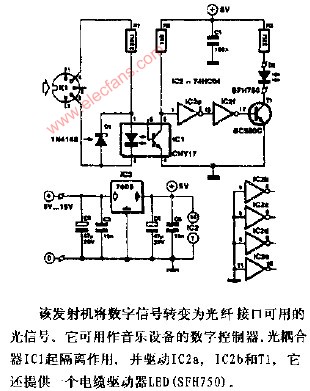

調制光發(fā)射機

作為光發(fā)射的一種方法,可以用音頻信號來調整燈絲����,

2009-09-18 17:31:51 828

828

音樂設備數(shù)字接口(MIDI)發(fā)射機

2009-09-28 12:04:01 907

907

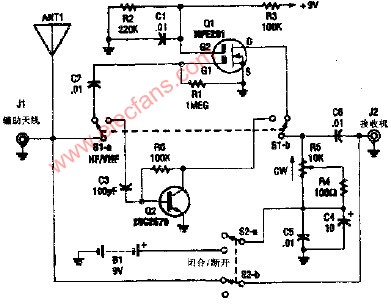

可轉換的HF VHF有源天線

AA-7型有源天線包含來那個個

2009-10-06 15:51:21 1935

1935

數(shù)字調諧濾波器原理及方案

0 引 言 需要傳送的數(shù)字或模擬信號信息一般是低頻信號,必須被載波調制到特定射頻段才能通過天線發(fā)射出去����。隨著通訊

2009-11-10 09:51:17 1419

1419

光發(fā)射器件,什么是光發(fā)射器件

一、直接調制激光發(fā)射機

1����、組成

直接調制光發(fā)

2010-04-02 15:58:40 1673

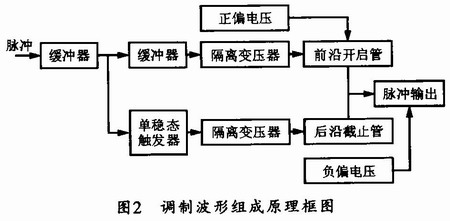

1673 O 引言

調制器是雷達發(fā)射機中的

2010-11-16 10:21:38 2470

2470

介紹了寬帶外調制模擬光發(fā)射機的設計,成功實現(xiàn)了寬帶外調制模擬光發(fā)射機����,其頻率響應1.5dB帶寬達到3GHz����,可用于雷達、微波等模擬信號的光發(fā)射

2011-02-14 17:58:52 52

52 本文以DFB直接調制光發(fā)射機為原型����,對光發(fā)射機的電路原理與常見故障進行了分析和探討。

2011-02-15 11:02:16 144

144 該發(fā)射機與信號采集電路采用數(shù)字接口����,利用雙路差分輸出數(shù)/模轉換電路AD9761產(chǎn)生基帶I/Q信號����,利用ADF4360-1鎖相環(huán)產(chǎn)生差分本振信號,利用AD8346進行差分正交調制����,采用差分電路提高了系統(tǒng)性能,

2011-02-19 09:38:42 4259

4259

摘要:設計了一種發(fā)射機中頻數(shù)字化方案.該方案的顯著特點是:調制方式����、調制速率����、中頻頻率皆可編程設置.鑒于美國Intersil公司推出的HSP50415數(shù)字上變頻可編程超大規(guī)模集成芯片的參考資料過于簡單的問題,介紹了Intersil公司數(shù)字上變頻器HSP50415的功能和特點,

2011-02-27 14:37:13 50

50 通信系統(tǒng)的振幅鍵控(ASK)����、移頻鍵控(FSK)和移相鍵控(PSK)是數(shù)字調制的3種基本信號形式。而數(shù)字調制器載波的產(chǎn)生通常都是基于查找表的方法����,為了達到高精度要求,需要耗費大量的RO

2011-04-27 11:15:43 57

57 本文首先介紹了 數(shù)字調制 誤差的概念,給出了LabVIEW調制工具包中PSK數(shù)字調制誤差測量模塊(MT Measure PSK Quadrature Impairments)工作原理����,然后以EVM測量為例分析了測量誤差,根據(jù)數(shù)字調制解調

2011-06-21 16:20:36 21

21 表征信號調制質量的數(shù)字調制參數(shù)是數(shù)字通信系統(tǒng)的主要技術指標, 數(shù)字調制 參數(shù)校準可以保證通信設備的質量。為給通信裝備數(shù)字調制參數(shù)校準工作提供技術支持, 本文總結研究了數(shù)

2011-06-21 18:01:53 52

52 諧振式光纖陀螺是采用環(huán)形諧振腔來增強薩格納克( Sagnac) 效應的,其數(shù)字閉環(huán)檢測方案具有動態(tài)范圍大,靈敏度高的特點����。對于雙頻率數(shù)字調制的諧振式光纖陀螺,該文提出了兩種基于數(shù)字

2011-09-13 14:39:45 34

34 介紹了常用的多進制數(shù)字調制技術及其應用,比較了它們的頻譜利用率和實現(xiàn)的難易,給出了多種數(shù)字調制的新技術.

2012-03-07 11:00:37 4269

4269 為了提高數(shù)字調制信號發(fā)生器的頻率準確度和穩(wěn)定度,并使其相關技術參數(shù)靈活可調����,提出了基于FPGA和DDS技術的數(shù)字調制信號發(fā)生器設計方法。利用Matlab/Simulink����、DSP Builder����、QuartusⅡ 3個

2013-04-27 16:50:59 183

183 介紹了一種以AD9957為核心器件的����、基于FPGA和DDS技術的通用數(shù)字調制器。詳細介紹了該器件的原理����、結構和使用方法,分析了PCM/FM����、PCM/DSSS/BSPK兩種調制方式的軟件設計,給出了一個利用

2013-09-25 16:05:21 62

62 標準����。在研發(fā)階段����、測試階段和制造階段,工程師們需要一臺儀器為被測器件測試生成標準和/ 或定制矢量/ 數(shù)字調制信號����。本文介紹了四種測試用例����,包括生成GFSK 信號����、生成WCDMA 信號、生成定制信號及生成超寬帶寬數(shù)字信號����,以及怎樣為每種用例生成矢量和數(shù)字調制信號。

2015-05-28 15:15:17 213

213 基奇AD9851型DDS的數(shù)字調制系統(tǒng)設計和實現(xiàn)

2016-02-19 17:09:00 33

33 本章介紹二進制及多進制數(shù)字調制系統(tǒng)原理����、抗噪性能、載波同步原理����,并將數(shù)字基帶系統(tǒng)中無碼間串擾條件、時域均衡����、眼圖����、位同步及最佳化等概念和結論應用到數(shù)字調制系統(tǒng)����。另外����,本章還對恒包絡調制原理進行簡單介紹����。

2016-06-23 16:53:00 0

0 電子專業(yè)單片機相關知識學習教材資料——使用數(shù)字示波器測量數(shù)字調制信號

2016-08-08 17:03:24 0

0 基礎RF數(shù)字調制技術

2017-09-19 08:40:05 9

9 1.。 項目名稱: HF/VHF數(shù)字調制多功能發(fā)射機 2.����。 項目的主要內容及目前的進展情況: 本項目主要的內容是:設計制作一臺能工作在HF及VHF波段的數(shù)字調制發(fā)射機,能提供AM����, FM����,DSB

2017-11-17 15:54:16 9

9 現(xiàn)代數(shù)字無線通信發(fā)射機的設計給設備設計者們帶來了越來越多的挑戰(zhàn)����。數(shù)據(jù)吞吐量不斷增長的趨勢����,使得所發(fā)射信號的調制密度和載波帶寬也隨之增加。在傳送相同有效值(rms)功率電平的信號時����,要保持良好的相鄰

2017-11-24 07:02:02 387

387

首先簡要介紹了射頻數(shù)字化短波發(fā)射機的基本原理以及AD9957芯片的主要功能,然后提出了一種利用AD9957芯片QDUC模式實現(xiàn)射頻數(shù)字化短波發(fā)射機內部數(shù)字上變頻模塊和數(shù)/模轉換模塊的方案����,對該模式

2018-05-01 15:13:00 4527

4527

本文主要介紹了簡易光發(fā)射機電路圖大全(晶振調頻/彩色電視/音頻發(fā)射機電路圖詳解)。光發(fā)射機是在發(fā)射端將電信號轉換成適合于在光纖中傳輸?shù)墓庑盘?���。光源是?b class="flag-6" style="color: red">發(fā)射機的主要器件,但僅有光源是不能構成發(fā)射機

2018-03-09 13:51:36 16413

16413

AD9853將高速直接數(shù)字合成器(DDS)����、高性能、高速數(shù)模轉換器(DAC)����、數(shù)字濾波器和其他DSP功能集成到單芯片上����,形成完整靈活的數(shù)字調制器器件����。AD9853旨在作為網(wǎng)絡應用中的調制器,如交互HFC����、WLAN和MMDS,其中成本����、尺寸、功耗����、功能集成和動態(tài)性能是關鍵屬性。

2018-06-19 08:00:00 0

0 本文檔的主要內容詳細介紹的是數(shù)字調制系統(tǒng)之基帶數(shù)字信號的表示與傳輸����。

2018-11-07 16:15:07 19

19 無論是模擬調制,還是數(shù)字調制����,都是采用調制信號去控制裁波信號的三要素:幅度、頻率和相位����,分別別稱為調幅、調頻和調相����。模擬調制稱為AM、FM和PM����,而數(shù)字調制稱為ASK、FSK和PSK����。數(shù)字調制中還有一種調制方式同時包含幅度和相位調制,稱為QAM調制(正交幅度調制)����。

2020-07-20 10:25:00 1

1 現(xiàn)代數(shù)字無線通信發(fā)射機的設計給設備設計者們帶來了越來越多的挑戰(zhàn)。數(shù)據(jù)吞吐量不斷增長的趨勢����,使得所發(fā)射信號的調制密度和載波帶寬也隨之增加。在傳送相同有效值(rms)功率電平的信號時,要保持良好的相鄰

2020-08-11 18:51:00 0

0 利用 Matlab作為編程工具����,對二進制數(shù)字調制系統(tǒng)進行了分析,設計了進制數(shù)字調制系統(tǒng)模型����,并對模型的仿真流程以及仿真結果進行具體分析,加強對理論知識的學習和掌握����。

2021-01-20 11:20:10 17

17 電子發(fā)燒友網(wǎng)站提供《數(shù)字調頻發(fā)射機開源項目.zip》資料免費下載

2023-06-09 14:29:41 4

4 這是一個小型電視發(fā)射機電路,具有VHF����,負聲音調制和PAL視頻調制。它適用于使用B和G系統(tǒng)的國家����。

2023-07-28 14:35:37 1580

1580

本文介紹VSA 的矢量調制分析和數(shù)字調制分析測量能力。某些掃頻調諧頻譜分析儀也能通過使用另外的數(shù)字無線專用軟件來提供數(shù)字調制分析����。然而,VSA 通常在調制格式和解調算法配置等方面提供更大的測量靈活性

2023-08-24 09:24:23 684

684

電子發(fā)燒友App

電子發(fā)燒友App

評論