的GPIO/中斷引腳��。在每個讀取周期中��,控制器都可以監(jiān)視ERR引腳的輸出��。當檢測到ERR引腳上的高電平時����,ASIC應啟動軟件子例程以重寫從SRAM讀取的正確數(shù)據(jù)��。圖6顯示了此方案的體系結構��。1.2寬度擴展

2020-10-23 11:32:38

基本正確��。外部可變的數(shù)據(jù)輸入fpga�����,通過spi也基本正確�,外部輸入變化,單片機接收的數(shù)據(jù)也會相應的變化�。測試SRAM時,參考網(wǎng)上的DE2開發(fā)板的SRAM例子�,往SRAM里寫固定的遞增數(shù)據(jù),然后由輸入

2013-07-24 22:41:55

的讀和寫端口�,設計里在每個數(shù)據(jù)引腳上以雙倍數(shù)據(jù)速率各自獨立地工作,因此能在一個時鐘周期中傳輸4個數(shù)據(jù)字�,因此4倍數(shù)據(jù)速率而得名。設計上采用分離的讀/寫端口從根本尚消除了SRAM與存儲控制器之間對總線爭用

2017-06-02 10:45:40

介紹的是關于SRAM的基礎模塊存有三種情況:standby(空余)���,read(讀)和write(寫)�。 第一種情況:standby假如WL沒有選為上拉電阻��,那么M5和M62個做為操縱用的晶體三極管處在

2020-09-02 11:56:44

介紹的是關于SRAM的基礎模塊存有三種情況:standby(空余)�����,read(讀)和write(寫)��。

2020-12-28 06:17:10

數(shù)據(jù)指針 在嵌入式系統(tǒng)的編程中�����,常常要求在特定的內存單元讀寫內容,匯編有對應的MOV指令�,而除C/C++以外的其它編程語言基本沒有直接訪問絕對地址的能力。在嵌入式系統(tǒng)的實際調試中�����,多借助C語言指針

2021-12-15 08:56:20

TFT LCD液晶顯示屏�、LY68L6400SLI SRAM芯片,對應的引腳如下:軟件設計QSPI SRAM測試初始化TFT LCD初始化QSPI SRAM寫數(shù)據(jù)到QSPI SRAM從QSPI

2022-05-27 19:52:05

CLA_CPU_MSGRAM 時����,還沒有寫完�,此時CPU中斷讀這個值,會不會出問題�����?反之CPU寫數(shù)據(jù)到 CPU_CLA_MSGRAM 時�����,還沒有寫完�����,此時CLA中斷讀這個值����,會不會出問題?

2018-10-17 15:01:23

什么是指針��?指針是變量�����。像其他變量一樣�����,它具有數(shù)據(jù)類型和標識符���。但是��,使用指針的方式與使用“普通”變量的方式根本不同���,并且必須使用星號告訴編譯器應該將變量視為指針�。這是指針聲明的兩個示例:char

2020-09-08 23:30:28

隨機存取存儲器(RAM)讀�����、寫隨機尋址數(shù)據(jù)丟失只讀存儲器(ROM)讀隨機尋址數(shù)據(jù)不丟失工作前寫入數(shù)據(jù) 閃存(Flash Memory)讀�����、寫隨機尋址數(shù)據(jù)不丟失先進先出存儲器(FIFO)讀����、寫順序尋址

2012-08-15 17:11:45

SRAM 在讀寫上有嚴格的時序要求,用 WEOECE 控制完成寫數(shù)據(jù)���,具體時序如圖 7-17所示�����。圖 7-17 SRAM 的寫時序系統(tǒng)中兩塊 SRAM 分別由 DSP 和 FPGA 控制����。當 DSP

2018-12-11 10:14:14

我現(xiàn)在需要統(tǒng)計sram的地址出現(xiàn)的頻率,比如如果地址1出現(xiàn)一次����,就在地址1里存1��,地址10出現(xiàn)了5次����,就在地址10里存5,其它地址也是進行類似操作��。��。���。本來準備是根據(jù)地址直接對這個地址進行寫1操作

2016-10-26 11:18:25

�����,這部分是寫數(shù)據(jù)�。就看寫的數(shù)據(jù)和sram_data是不是一樣的����,發(fā)現(xiàn)是一樣的�����。說明功能正確���。然后觀察黃線右邊的部分,這部分是讀數(shù)據(jù)�。就看讀的數(shù)據(jù)是不是和sram_data_reg一樣的。發(fā)現(xiàn)

2015-03-19 20:17:25

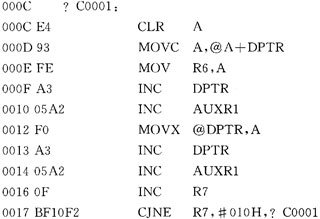

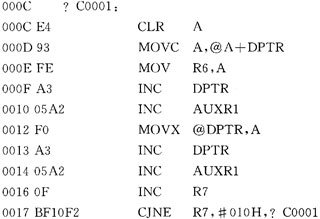

的性能�。作為一種增強特性,有許多8051派生型器件支持雙數(shù)據(jù)指針���。以宏晶科技STC89系列的產(chǎn)品為例�,DPTR被增強為DPTR0和DPTR1兩個�,仍然使用原來的地址,用另外一個SFR AUXR1的0位

2011-11-30 17:30:00

順序寫入數(shù)據(jù),亂序寫入數(shù)據(jù)�����,直接填充數(shù)據(jù)都是正常的���。在程序中使用指針操作時����,如果地址%64<32,改變這個地址的數(shù)據(jù)��,也會改變這個地址+32的數(shù)據(jù)��。如果地址%64>

2023-03-28 08:13:08

的標稱性能��。雙模結構如圖1所示�。標準模式標準模式是標準接口的一個配置選項����,在這種模式下,為了節(jié)省必須從內核發(fā)送的信號總數(shù)����,I-SRAM和D-SRAM信號合并在一起。除了數(shù)據(jù)寫總線外����,D-SRAM接口

2019-05-28 05:00:02

應用:數(shù)據(jù)閃光模擬EEPROM和寫/讀EEPROM

BSP 版本:Mini51DE系列 BSP CMISIS V3.02.000

硬件: NuTiny-EVB-Mini51_V2.1

使用數(shù)據(jù)閃電

2023-08-30 07:54:52

嗨,我寫了一個軟件��,將數(shù)據(jù)寫入FPGA寄存器,并讀取處理結果�����。我發(fā)現(xiàn)重復讀/寫��,軟件再也無法讀取寄存器(DpcPutReg函數(shù)返回-1)我也嘗試使用Adept軟件����,經(jīng)過一些(10~30)讀/寫后,我

2019-07-22 08:14:21

����。FIFO選用了IDT公司的IDT7202。它具有輸入和輸出兩套數(shù)據(jù)線�,獨立的讀/寫地址指針在讀/寫脈沖的控制下順序地從雙口FIFO讀/寫數(shù)據(jù),讀/寫地址指針均從第一個存儲單元開始���,直到最后一個存儲單元

2019-04-26 07:00:06

的IDT7202�����。它具有輸入和輸出兩套數(shù)據(jù)線����,獨立的讀/寫地址指針在讀/寫脈沖的控制下順序地從雙口FIFO讀/寫數(shù)據(jù),讀/寫地址指針均從第一個存儲單元開始�����,直到最后一個存儲單元��,然后又回到第一個存儲單元

2018-12-05 10:13:09

0xC1FFFFFF遍歷寫入并讀出,通過TIM2計時,以字節(jié)寫入時,寫時間0.16秒,讀時間0.73秒,以半字節(jié)操作時,寫時間0.09秒,讀時間0.71秒���。請問為什么讀比寫要慢得多����?

下面是寫入和讀出代碼�,系統(tǒng)主頻550M�,邏輯操作耗時應該基本可以忽略

for(temp=0; temp

2024-03-11 06:40:14

與SRAM芯片連接。 SRAM型號IS62WV51216��,管腳圖如下: IS62WV51216的管腳總的來說大致分為:電源線�����、地線�����、地址線、數(shù)據(jù)線��、片選線�、寫使能端、讀使能端和數(shù)據(jù)掩碼信號線

2020-05-07 15:58:41

1. 程序和數(shù)據(jù)在Flash和SRAM上的存儲結構在講解 STM32 啟動過程之前�����,我們先來了解一下 STM32 的程序和數(shù)據(jù)在 Flash 和 SRAM 上到底是如何存儲的����,因為有了這方面的知識

2022-02-18 06:13:34

接口對于SRAM的讀操作時序,其波形如圖所示����。對于SRAM的寫操作時序,其波形如圖所示�。具體操作是這樣的,要寫數(shù)據(jù)時����,(這里是相對于用FPGA操作SRAM而言的,軟件讀寫可能有時間順序的問題需要

2015-12-16 12:46:04

實例每秒鐘定時進行一個SRAM地址的讀和寫操作�。讀寫數(shù)據(jù)比對后����,通過D2 LED狀態(tài)進行指示����。與此同時,也可以通過chipscope pro在ISE中查看當前操作的SRAM讀寫時序�。 2 模塊劃分該

2015-12-18 12:57:01

在SRAM中存滿數(shù)據(jù),并通過以太網(wǎng)發(fā)送滿盤數(shù)據(jù)�。發(fā)送時也是像例程一樣,定義數(shù)據(jù)數(shù)組����,讀一個SRAM地址指針更新一次數(shù)據(jù)數(shù)組?還是有其他方法���?

2019-07-01 04:35:46

使用MCU的FMC外擴SRAM時���,對外部SRAM進行讀寫操作時�,寫操作無異常,通過寄存器均可按照手冊控制����。在進行讀操作時�,開啟EXTMOD功能�,即使總線周轉時間設置為0,兩次連續(xù)的讀操作時間還為

2018-08-23 08:51:05

都是低電平有效���,后綴_n用于強調這一特性���。功能表如表1所示:信號ce_n用于存儲器擴展,信號we_n和oe_n用于寫操作和讀操作�,lb_n和ub_n用于字節(jié)配置。 表1 SRAM控制信號的真值表接下來

2017-03-07 16:26:01

���,比如讀��、寫�、調用函數(shù)等����。 2、永遠不要使用“野”指針 前面說了��,指針的內容是 地址,是內存地址����,一旦你擁有了一個指針,你也就有了權力去通過這個指針名字去訪問指針指向的內容了�����,我們可以打個比方��,內存

2019-08-20 08:30:00

寫入相應的數(shù)據(jù)�。2、(2級) sram的讀寫操作要求:1��、每隔1s對sram讀一次����,每次讀取一個數(shù)據(jù),讀地址每次增加1(0--1---�、、�、--15--0)�,2、寫數(shù)據(jù)要求:在不影響sram讀的情況下

2015-05-09 10:41:41

這里寫自定義目錄標題為什么要擴展外部SRAM(一)什么是SRAM簡介存儲器型號容量引腳配置通訊方式讀寫特性讀取數(shù)據(jù)時序圖讀取數(shù)據(jù)的時序要求寫入數(shù)據(jù)時序圖寫入數(shù)據(jù)的時序要求(二)什么是FSMC外設簡介

2021-08-05 07:13:19

這里寫自定義目錄標題(一)為什么要擴展外部SRAM(二)什么是SRAM簡介 存儲器型號 容量 原理框圖 引腳配置 通訊方式 讀寫特性 讀取數(shù)據(jù)時序圖 讀取數(shù)據(jù)的時序要求 寫入數(shù)據(jù)時序圖 寫入數(shù)據(jù)

2021-08-05 08:22:50

尋址的存儲單元將它存儲的數(shù)據(jù)送到相應位線上的操作��。圖3.5 表示的是進行讀操作的一個SRAM單元,兩條位線開始都是浮空為高電平����。假設當前單元中存儲的值為邏輯“1”,即節(jié)點A為高電平��,節(jié)點B為低電平

2020-04-29 17:27:30

這是網(wǎng)上比較流行的一個異步fifo方案��,但是fifo的空滿判斷不是應該是立即的嗎�����,加上同步器之后變成寫指針要延時兩個讀周期再去個讀指針做空比較����,而讀指針要延時兩個寫周期再去和寫指針做滿比較,這樣雖然可以避免亞穩(wěn)態(tài)之類的問題�����,可是這個延時對總體的空滿判斷沒有影響嗎��,如果沒有影響是怎么做到的呢,求解

2016-07-24 16:25:33

已用這種模式成功驅動了一些psram��,但是SRAM始終驅動不了��。

SRAM驅動架構

XMC復用模式讀時序��,其中一個HCLK=4.16ns(240Mhz)

SRAM讀時序參數(shù)

SRAM讀時序圖

XMC

2024-01-04 10:46:19

SRAM接口對于SRAM的讀操作時序�,其波形如圖8.36所示�����。圖8.36 SRAM讀時序對于SRAM的寫操作時序,其波形如圖8.37所示����。圖8.37 SRAM寫時序具體操作是這樣的,要寫數(shù)據(jù)時��,(這里是

2018-05-03 21:02:25

其應用范圍���,難壞了一大幫業(yè)余科學實驗家��。 今這小亮一“讀SD卡圖形直接寫屏”的非常規(guī)招式�����,不占SRAM內存了��、代碼量減少了��、速度加快了����、低階的單片機也能引用了�,這可是“鼠輩得翼成仙”的節(jié)奏,非同小可

2017-07-31 12:52:13

的寄存器����,例如:#define DDRB (*(volatile unsigned char *)0x25)分析如下:這樣讀/寫以0x25為地址的SRAM單元,直接書寫DDRB即可�����,即DDRB...

2021-11-30 08:07:19

SRAM 單元[17]����,如圖 3 所示。這種結構具有獨立的讀寫字線(RWL, WWL)和讀寫位線(RBL, WBL 和 WBLB)�,從而有分開的讀端口和寫端口;數(shù)據(jù)從讀端口讀出,從寫端口寫入�����。這樣不僅

2020-07-09 14:38:57

你好�����,我有一個設計使用SRAM塊����,我想用一組輸出寄存器配置它們。這通常會在讀取操作中引入額外的延遲周期�����。但是�����,如果系統(tǒng)的其余部分以50MHz的頻率運行�,那么我可以將SRAMat設置為100MHz

2019-07-03 12:51:27

};pthread_mutex_lock(&mut);//考慮到485是半雙工�,讀的時候不能寫,寫的時候不能讀����,故加鎖控制sendCmdToSerial(sendData, sizeof(sendData

2016-10-14 14:22:24

在MCU(以常見的stm32為例)開發(fā)中使用多線程操作,我們經(jīng)常遇到的問題是關于多線程訪問數(shù)據(jù)的問題�����,多線程訪問數(shù)據(jù)基本上可以分為幾大類:多寫一讀多寫多讀一寫多讀一寫一讀多線程中如果出現(xiàn)多寫�,數(shù)據(jù)

2023-02-01 15:42:35

僅僅優(yōu)化了單元讀、寫一方面的性能,另一方面保持不變或者有惡化的趨勢;單端讀寫單元往往惡化了讀寫速度,并使靈敏放大器的設計面臨挑戰(zhàn);輔助電路的設計,往往會使SRAM的設計復雜化���。 為了使SRAM存儲單元

2020-04-01 14:32:04

了�,并繼之以讀使能校準���。讀使能邏輯對向存儲器發(fā)送的讀命令進行校準�,為已采集到并寫入讀數(shù)據(jù) FIFO 的數(shù)據(jù)生成寫使能���。校準邏輯使用 SRL16 構建而成���,有助于確定讀命令信號所需寄存器級數(shù)的數(shù)量���,以

2019-04-22 07:00:07

我的目標是讀/寫8位數(shù)據(jù)到SRAM芯片AS6C4008。有點像尼古拉斯·維南2011A年5月在硅芯片上的SPORTSYNC項目����,兩周后仍然不能工作:1。我已經(jīng)檢查了所有的線路2����。所有的MCU引腳都能

2019-10-11 07:31:13

(__IO uint16_t*)(0x60000000)將內部地址強制轉換成了8位和16位的指針����,這又是為什么?這個指針指向的不是內部SRAM的地址嗎����?如果是,這樣子轉換不會導致數(shù)據(jù)丟失嗎��,如果不是���,這個指針又是指向哪里���?難道是直接映射到外部SRAM里面了嗎���?懇請求教,十分感謝�!

2022-08-19 01:08:14

Rev2S25FL256L:002-00124 版本 * H 我目前正在使用H723創(chuàng)建一個讀寫NORFLASH的項目���。 但是�,讀/寫不成功����。 我想以H723為主��,外接flash為從進行讀寫���。 1���、CubeMX設置不正確

2022-12-27 06:38:05

你好�����,我正在做一個使用GPIF II接口作為主機來從SRAM中寫入和讀取數(shù)據(jù)的項目。在我的固件項目中���,DMA大小是512���,計數(shù)是2。我已經(jīng)成功地測試了寫和讀數(shù)據(jù)不到1024BIT����。并且知道我想要像

2019-09-25 14:56:47

NUC472/NUC472/NUC442系列裝有外部連接設備的外部公交界面(EBI)。 NUC472/NUC442 EBI便利連接控制界面由地址��、數(shù)據(jù)��、芯片選擇和讀/寫斯特羅貝組成的設備,例如NOR閃光

2023-08-23 06:35:44

請問一下影響編程時間的因素是什么�?如何減少寫編程時間和讀等待時間以提高讀寫性能呢��?

2021-06-21 07:21:06

的值和*a的值都輸出�,這時候printf輸出的a就是一串數(shù),十進制的����,而*a就是b的值�����,這時候我有個疑問���,這個指針變量是以什么形式保存,或者說所有變量類型��,我們可不可以以十進制直接保存��,然后讓他以指針

2019-11-05 03:40:28

如何對RAM進行讀和寫的操作��?

2022-01-18 06:47:23

大家好����,我正在嘗試使用Nexys-3板設計PDP-8內存��。但我正在努力弄清楚如何使用板上的CellularRAM來讀/寫�。我在Google上找不到任何有用的信息��。有人能給我一個關于如何用

2019-07-01 08:50:31

我正在使用SPC560D和SPC5Studio�����。我想在將設備置于待機模式之前保存設備配置/狀態(tài)�,并在設備退出待機模式時使用/檢索此狀態(tài)。這可以通過使用SRAM來實現(xiàn)嗎���?如何訪問SRAM以進行可變存儲

2019-06-21 08:53:02

如圖所示的異步FIFO�,個人覺得在讀寫時鐘同步時會產(chǎn)生兩個時鐘周期的延時���,如果讀寫時鐘頻率相差不大���,某一時刻讀寫指針相等,當寫指針同步到讀模塊時會產(chǎn)生延時����,實際同步到讀模塊的寫指針是兩個時鐘周期之前的,這樣就不會產(chǎn)生空滿信號��,要兩個周期之后才能產(chǎn)生空滿信號,結果是寫溢出或讀空

2015-08-29 18:30:49

本帖最后由 一只耳朵怪 于 2018-6-14 10:51 編輯

我想往CPU1TOCPU2RAM寫一組數(shù)據(jù)���,CPU2來讀���,如何來判斷這一組數(shù)據(jù)讀時已寫完?可不可以用這個呢�?

2018-06-14 04:20:16

我正在使用 S32k358 uC��,我想禁用內存區(qū)域的數(shù)據(jù)緩存�。在框圖中,我看到樹形 SRAM 塊 SRAM0�����、SRAM1����、SRAM2。是否可以禁用 SRAM2 的數(shù)據(jù)緩存并保留 SRAM 0 和 SRAM1 的數(shù)據(jù)緩存�?

2023-04-23 08:01:09

靜態(tài)存儲單元和其讀寫控制電路組成的記憶體電路,對此的詳細內容在四個晶體管搭建靜態(tài)存儲單元��,加兩個晶體管搭建寫控制電路一文中���。LY62L5128是一個CMOS SRAM��。容量512KB(512K X 8

2016-08-30 04:32:10

谷歌和這個論壇沒有返回太多關于在 8 位模式下直接訪問 GPIO 端口以進行讀/寫的信息......例如控制一個 8 位 TFT 模塊......HAL 庫也沒有它的功能....我認為這是可能的..但只有在深入研究低級直接寄存器訪問時才有可能���?

2023-02-07 06:25:37

請教各位大神講解下如何用ActiveX控件與Excel實現(xiàn)數(shù)據(jù)讀��、寫�?

2014-03-27 19:49:20

親愛的,流水線SRAM的數(shù)據(jù)表(例如部分CY7C1382KV33)在第8頁的“單讀訪問”段落中表示����,支持連續(xù)的讀周期����。一個讀周期有一個延遲2個時鐘周期��。這是否意味著你可以每2個CLK周期做一個讀周期

2018-08-16 04:11:48

用FPGA往SRAM芯片中寫數(shù)據(jù)重復寫多次才能寫是怎么回事呢?

2023-04-23 11:46:44

單片機和LCD1602的讀狀態(tài)�,寫狀態(tài)�,讀數(shù)據(jù),寫數(shù)據(jù)各指的什么����,不是太明白,請高手幫忙解答����,謝謝

2019-04-12 06:35:22

STM8讀同時寫RWW

2020-11-10 07:20:30

F207VE-26ms/1Mbytes���;實測寫速度:F103VC-43.5ms/1Mbytes F207VE-27.3ms/1Mbytes(7)要使用SRAM��,定義1個這樣的指針:static U32 *aMemory = (U32 *)FSMC_BANK1_1_NE1;(8)有時間的話了解下我們的人機界面解決方案GLCD

2016-07-08 15:10:32

SRAM,SRAM原理是什么?

靜態(tài)隨機存取存儲器SRAM��。

SRAM主要用于二級高速緩存(Level2 C ache)����。它利用晶體管來存儲數(shù)據(jù)����。與DRAM相比,SRAM的速度快

2010-03-24 16:11:32 8479

8479 在8051體系中��,數(shù)據(jù)指針DPTR作為一個特殊的16位寄存器����,用于尋址64 KB的XDATA或CODE空間����,通常它被當作一個16位指針�,指向一個常數(shù)表。雙數(shù)據(jù)指針可以改善同時有兩個16位指針使用時

2010-07-20 17:36:46 1276

1276

STM32單片機上的SRAM 中的數(shù)據(jù)丟失

2015-11-25 14:49:27 0

0 C和指針習題答案配C和指針

2017-09-07 14:29:48 6

6 SRAM不需要刷新電路即能保存它內部存儲的數(shù)據(jù)�。而DRAM(Dynamic Random Access Memory)每隔一段時間,要刷新充電一次��,否則內部的數(shù)據(jù)即會消失�����,因此SRAM具有較高的性能���,功耗較小�����。

2017-11-03 16:11:12 11253

11253 首先���,你要明白一個概念����,指針���,是做什么的?答案是�,指針,是指向地址的��。程序指針�,指向的空間,在物理上是Flash����,在邏輯上,就是代碼空間����。比如說51單片機的PC指針,指向的就是Flash����,即程序下一步要執(zhí)行的指令的地址。

2017-11-10 11:21:57 7418

7418

堆棧指針總是指向棧頂位置���。一般堆棧的棧底不能動��,所以數(shù)據(jù)入棧前要先修改堆棧指針����,使它指向新的空余空間然后再把數(shù)據(jù)存進去,出棧的時候相反�。堆棧指針,隨時跟蹤棧頂?shù)刂?���,按“先進后出”的原則存取數(shù)據(jù)。

2017-11-13 09:40:17 12736

12736

為什么使用指針�?因為在操作大型數(shù)據(jù)和類時,指針可以通過內存地址直接訪問數(shù)據(jù)�,可避免在程序中復制大量的代碼,因此指針的效率最高����。一般來說,指針會有3大用途

2018-10-04 10:33:00 4720

4720 SRAM主要用于二級高速緩存����。它利用晶體管來存儲數(shù)據(jù)���。與DRAM相比,SRAM的速度快�,但在相同面積中SRAM的容量要比其他類型的內存小。

2019-04-01 16:28:47 9613

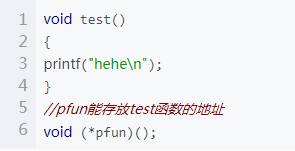

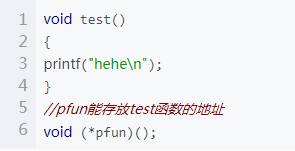

9613 理解函數(shù)指針���、函數(shù)指針數(shù)組、函數(shù)指針數(shù)組的指針

2020-06-29 15:38:34 14291

14291

一種由普通SRAM、后備電池以及相應控制電路集成的新型存儲器:非易失性SRAM(NVSRAM)��。 為解決SRAM的數(shù)據(jù)保存問題���,國外著名半導體公司率先推出了可以完全替代SRAM的NV-SRAM系列產(chǎn)品�����,國內也有同類產(chǎn)品相繼問世���。面對眾多的NVSRAM產(chǎn)品����,廣大用戶如何選擇質優(yōu)價廉的產(chǎn)品呢���?建議用戶根據(jù)以

2021-01-11 16:44:20 1714

1714 C語言指針的理解使用指針變量的聲明給普通變量的賦值對比給指針變量的賦值代*的指針的使用說明指針變量的聲明一個指針聲明后沒有賦值����,它的數(shù)據(jù)位是隨機的:unsigned char *p�;給一個指針變量

2022-01-13 13:42:25 3

3 在C語言中一個數(shù)組,若其元素均為指針類型數(shù)據(jù)��,稱為指針數(shù)組�����,也就是說���,指針數(shù)組中的每一個元素都存放一個地址�,相當于一個指針變量。

2023-03-10 15:26:24 1140

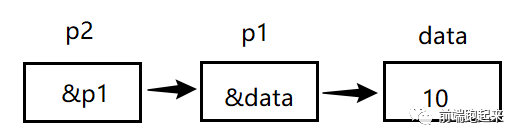

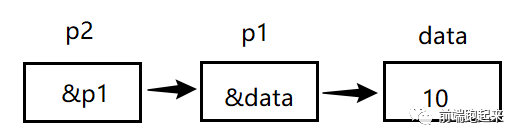

1140 一級指針的用法其實是取數(shù)據(jù)的地址,以此類推����,二級指針就是取一級指針的地址,也可以表示一級指針的指向的內容��。

2023-05-19 17:30:29 863

863

SRAM可以分為低速����、中速����、高速。===========================================================16位寬的SRAM//16BITSRAM指針

2023-04-06 15:13:03 554

554

電子發(fā)燒友App

電子發(fā)燒友App

評論