聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權轉載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學習之用,如有內(nèi)容侵權或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

Altera

+關注

關注

37文章

774瀏覽量

153809 -

性能

+關注

關注

0文章

270瀏覽量

18950

發(fā)布評論請先 登錄

相關推薦

給Altera Arria 10 FPGA和Arria 10 SoC供電:經(jīng)過測試和驗證的電源管理解決方案

尺寸、重量和復雜性,并可降低功耗和冷卻成本。而且,它對于實現(xiàn)最優(yōu)系統(tǒng)性能是必不可少的。例如,從 12V DC/DC 穩(wěn)壓器提供 0.95V/105A 以給圖 1 的 Arria 10 GX FPGA

發(fā)表于 10-29 17:01

Intel Arria 10 GX FPGA供電4相降壓穩(wěn)壓器設計

描述A 4 phase buck regulator design fully complaint to power the core rail of Intel Arria 10 GX FPGAs

發(fā)表于 12-06 11:44

Altera的Arria 10版Quartus II軟件為立即開始20 nm設計提供支持

20 nm工藝技術,Arria 10 FPGA和SoC性能比目前的高端FPGA高出15%,功耗比以前的中端器件低40%,重塑了中端FPGA和SoC??蛻衄F(xiàn)在可以在熟悉而且成熟的Quartus II設計環(huán)境中,開始開發(fā)基于

發(fā)表于 12-03 10:48

?1731次閱讀

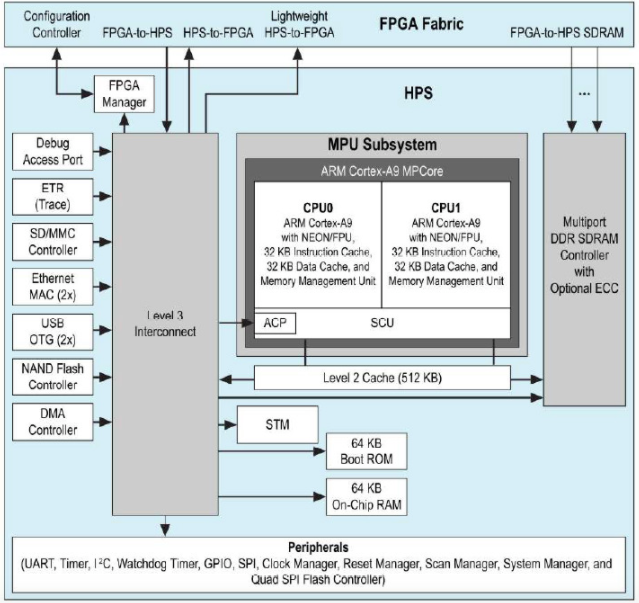

基于Arria 10 SoC FPGA的高性能低成本解決方案

本文介紹了Arria 10 SoC FPGA主要特性,框圖以及Arria 10 SoC開發(fā)板主要特性,電源分布網(wǎng)絡圖和電路圖。

介紹Arria II GX的特點性能及應用

能夠:

了解這一功耗和成本不到競爭高端FPGA的一半,卻具有高性能架構的FPGA。

了解運行PCI Express、XAUI和3G-SDI的Arria II GX收發(fā)器,查看收發(fā)器眼圖。

了解新的開發(fā)套件,您可以利用它來評估

英特爾Arria 10 SOC FPGA開發(fā)板硬件支持32位 DDR4 SDRAM

,廣泛的ARM軟件和工具生態(tài)系統(tǒng)以及增強的FPGA和數(shù)字信號處理(DSP)硬件設計流程。Arria 10 SoC旨在滿足中端應用的性能和功耗要求. 英特爾 Arria

發(fā)表于 05-20 14:05

?1426次閱讀

英特爾Arria 10 FPGA的應用之路

可提供中端市場中的最佳性能和能效。英特爾 Arria 10 FPGA 和 SoC 的高性能邏輯結構,結合了適用于芯片至芯片和芯片至模塊接口、

Arria 10 SoC確保系統(tǒng)設計滿足現(xiàn)在和未來性能要求

借助 Arria 10 SoC,您可以通過將 GHz 級處理器、FPGA 邏輯和數(shù)字信號處理 (DSP) 集成到單個可定制的片上系統(tǒng)中來減小電路板尺寸,同時提高性能。

基于Arria 10 SoC的控制模塊設計

因此,英特爾 Arria 10 SoC 為嵌入式外設、硬核浮點 DSP 模塊、嵌入式高速收發(fā)器、硬核存儲器控制器和協(xié)議 (IP) 控制器提供了具有廣泛功能范圍的處理器。

發(fā)表于 08-15 11:31

?529次閱讀

Arria? 10 的性能

Arria? 10 的性能

評論