在FPGA 上設(shè)計(jì)一個(gè)高性能�、靈活的、面積小的通信體系結(jié)構(gòu)是一項(xiàng)巨大的挑戰(zhàn)�。大多數(shù)基于FPGA 的片上網(wǎng)絡(luò)都是運(yùn)行在一個(gè)單一時(shí)鐘下�����。隨著FPGA 技術(shù)的發(fā)展����,Xilinx 公司推出了Virtex-4 平臺(tái)

2011-10-21 16:13:51 1270

1270

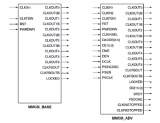

針對(duì)不同類型的器件�,Xilinx公司提供的全局時(shí)鐘網(wǎng)絡(luò)在數(shù)量、性能等方面略有區(qū)別�����,下面以Virtex-4系列芯片為例����,簡(jiǎn)單介紹FPGA全局時(shí)鐘網(wǎng)絡(luò)結(jié)構(gòu)。

2013-11-28 18:49:00 12149

12149

器件中選型�����。Xllinx公司的主流器件有Spartan-3E��、Spartan-3A����、Virtex-4LX、Virtex-4 SX�����、Virtex-4 FX�����、Virtex-5 LX���、Virtex-5SX

2020-11-19 15:39:56 4945

4945

賽靈思公司今天宣布推出全球最大容量的 FPGA – Virtex UltraScale+ VU19P����,從而進(jìn)一步擴(kuò)展了旗下 16 納米 (nm) Virtex? UltraScale+? 產(chǎn)品系列����。

2019-08-24 09:09:07 3390

3390 描述PMP9475 12V 輸入?yún)⒖荚O(shè)計(jì)以緊湊高效的設(shè)計(jì)提供為 Xilinx's Virtex? Ultrascale? 系列 FPGA 供電時(shí)所需的所有電源軌。此設(shè)計(jì)使用幾個(gè) TI 的 PMBus

2018-08-29 08:33:47

VIRTEX-4 - Tri-Mode Embedded Ethernet MAC Wrapper v4.4 - Xilinx, Inc

2022-11-04 17:22:44

VIRTEX-5FPGA - DC and Switching Characteristics - Xilinx, Inc

2022-11-04 17:22:44

親愛的社區(qū)成員�,我正在實(shí)施XAPP861中推薦的8x過采樣和數(shù)據(jù)恢復(fù)單元(DRU),以便在Virtex-4 FPGA上進(jìn)行異步串行數(shù)據(jù)恢復(fù)���。我通過3米DVI電纜接收了160bbps的8b10b編碼流

2020-06-18 16:00:28

嗨,我對(duì)Virtex-4中BRAM的工作頻率有疑問���。如果有人知道BRAM的最大工作頻率是多少���?提前致謝以上來自于谷歌翻譯以下為原文hi, I have a question about

2018-10-10 11:53:12

嗨��,我需要Virtex-4器件“xc4vfx12”的門數(shù)值����。如果有任何公式,我們可以用它來計(jì)算設(shè)備的可用門數(shù)����。 CLBS,切片和其他資源����,請(qǐng)告訴我。感謝致敬���,的Sandip

2020-06-18 07:02:27

嗨����,XilinxIDF站點(diǎn)表明IDF僅支持Virtex-4��,Virtex-5����,Spartan-6和7系列FPGA。我可以在Xilinx Virtex-6 FPGA上使用IDF嗎����?有沒有人嘗試過使用IDF和Virtex-6 FPGA?謝謝�,季米特里斯

2020-07-08 15:56:53

,正在發(fā)展中��,尚屬情理之中�����,如有需要可聯(lián)系小弟���,謝謝各位大俠支持支持 我司經(jīng)營(yíng)XILINX全系列產(chǎn)品����,包括VIRTEX-5,VIRTEX-II,VIRTEX-4,VIRTEX

2009-06-20 00:31:27

Xilinx FPGA:Virtex-II基本架構(gòu)

2012-08-02 23:12:34

本帖最后由 mr.pengyongche 于 2013-4-30 02:56 編輯

Xilinx Virtex-4 ML403嵌入開發(fā)平臺(tái)原理圖[url=www.0404.cc]

2012-08-17 09:12:44

你好,Xilinx Virtex 5 FPGA可以接受邏輯電平0 / 1.8V的輸入并提供邏輯電平0 / 3.3V的輸出嗎�����?謝謝���。asenapati以上來自于谷歌翻譯以下為原文Hello, Can

2018-10-29 14:19:38

描述 PMP9408 參考設(shè)計(jì)提供為 Xilinx 的 Virtex? Ultrascale? FPGA 中的千兆位收發(fā)器 (MGT) 供電時(shí)所需的所有電源軌����。它利用一個(gè) PMBus 接口來實(shí)現(xiàn)電流

2022-09-21 07:56:06

描述PMP9408 參考設(shè)計(jì)提供為 Xilinx 的 Virtex? Ultrascale? FPGA 中的千兆位收發(fā)器 (MGT) 供電時(shí)所需的所有電源軌����。它利用一個(gè) PMBus 接口來實(shí)現(xiàn)電流

2018-08-29 08:42:24

描述PMP10520 參考設(shè)計(jì)提供為 Xilinx 的 Virtex? Ultrascale? FPGA 中的千兆位收發(fā)器 (MGT) 供電時(shí)所需的所有電源軌(1V/20A、 1.2V/30A

2022-09-27 06:46:35

Virtex-4 XC4VFX12)����。之后,我想將它移植到新平臺(tái)(即Virtex-5 XC5VFX70T)����,但我的ISE Foundation 10.1安裝不支持這個(gè)FPGA。我錯(cuò)過了什么嗎��? ISE

2018-11-15 11:30:24

器件結(jié)構(gòu)及描述3.1 概述3.2 Spartan-ⅡE系列FPGA3.3 Spartan-3系列FPGA3.4 本章小結(jié)第4章 ISE 6.x設(shè)計(jì)工具簡(jiǎn)介和使用4.1 概述4.2 Xilinx設(shè)計(jì)流程

2012-02-27 14:43:30

你好�����,什么是運(yùn)行EDK�,Xilinx編程ML410或Virtex-4的最佳或至少可接受的要求����?至于CPU速度,內(nèi)存和磁盤容量��?我現(xiàn)有的系統(tǒng)運(yùn)行EDK樣品需要45分鐘以上�!問候,Ramsin

2020-06-02 15:10:59

* Virtex-II pro: 基于VirtexII的結(jié)構(gòu),內(nèi)部集成CPU和高速接口的FPGA產(chǎn)品 * Virtex-4: xilinx最新一代高端FPGA產(chǎn)品��,包含三個(gè)子系列:LX�,SX,F(xiàn)X 簡(jiǎn)評(píng)

2018-08-20 09:52:02

親愛的先生,我們已經(jīng)在我們的定制設(shè)計(jì)板上組裝了Virtex-4 FPGA BGA封裝��,組裝后我們進(jìn)行物理檢查時(shí)檢查所有電源接地之間是否短路�。請(qǐng)告訴我們調(diào)試此問題的任何過程并刪除簡(jiǎn)短����。 FPGA的穩(wěn)壓器電路與FPGA IC隔離問候薩蒂亞

2020-06-19 07:42:07

的bitgen以及SEM IP內(nèi)核可以做到這一點(diǎn)���,但據(jù)我所知它們不能與virtex-4一起使用����。有沒有其他方法來估計(jì)virtex-4器件(XQR4VS??X55??)的基本位���,以及我們?nèi)绾斡?jì)算同一器件的軟

2019-02-26 10:24:45

連接的設(shè)備及其相應(yīng)的設(shè)備ID����。 現(xiàn)在�,為了配置FPGA器件,我找到了Virtex-4系列的步驟��,但它們恰好與Spartan 3E的步驟略有不同。那么����,任何人都可以讓我知道Spartan 3E系列FPGA

2019-06-12 09:45:38

進(jìn)行比較,因此我可以獲得應(yīng)用程序和設(shè)備����。 Xilinx FPGA的特征信息����。Virtex-5的Virtex-4的Virtex-II Pro的Virtex-II的Virtex-E的Virtex

2019-05-08 14:52:17

Stratix III FPGA與Xilinx Virtex-5的體系結(jié)構(gòu)對(duì)比Stratix III FPGA與Xilinx Virtex-5的性能對(duì)比

2021-05-07 07:00:14

Xilinx Virtex-II Pro 和 Virtex-II Pro X 器件能提供集成 PowerPC 內(nèi)置技術(shù)的 FPGA,也是第一個(gè)能提供支持從 622 Mbps 到 10.3125

2013-09-06 16:28:27

系列主要應(yīng)用于通訊領(lǐng)域[1]�����;Xllinx公司的主流器件有Spartan-3E�,Spartan-3A,Virtex-4LX����,Virtex-4 SX,Virtex-4 FX��,Virtex-5 LX

2012-02-22 13:58:51

嗨�����,我讀了一篇使用Virtex SX35的論文����。它有一個(gè)關(guān)于使用資源的表格。我無法弄清楚RAM 16s的含義����。你可以幫幫我嗎?謝謝�����,

2020-06-18 09:56:44

當(dāng)我使用Actel FPGA中實(shí)現(xiàn)的簡(jiǎn)單擦洗保護(hù)Virtex4SX55時(shí)遇到問題����。如果我選擇“-g ReadBack”和“-g persist”選項(xiàng)����,則Virtex4SX55中的程序?qū)⒈籄ctel

2020-06-19 10:36:59

你好�,我是一名大學(xué)生����,我需要使用ISE處理Virtex 5 LX110T FPGA。為什么ISE WebPack中沒有可用的選項(xiàng)�����?以上來自于谷歌翻譯以下為原文Hello, I am a

2018-12-11 11:29:01

你好���, 我做了一個(gè)關(guān)于回讀virtex-4 FPGA的項(xiàng)目。 我想只使用沒有.msk文件的CRC-32進(jìn)行CRC校驗(yàn)���,當(dāng)然��,我只回讀MGT�����,CLB��,IOB��,DSP���,CLK����。無論FPGA工作與否����,我認(rèn)為這些都不可變。這是正確的��?并告訴怎么做����? 非常感謝!

2020-06-08 08:48:59

�����。我是否需要單獨(dú)執(zhí)行一個(gè)項(xiàng)目并僅實(shí)例化UART_TX EDIF文件��,并創(chuàng)建宏符號(hào)�?是否更新該文件以某種方式在Virtex-4上工作?Isit更容易禁用RLOC嗎��?我打算這樣做�����,但是有一個(gè)留言板帖子說

2020-05-27 07:57:19

我們?nèi)绾问褂?b class="flag-6" style="color: red">Virtex-4 FPGA的Block-RAM來存儲(chǔ)矩陣/ Vector的內(nèi)容����。例如����,如何在BRAM中存儲(chǔ)矢量A = [1 2 4 5 6 7 9 3]?OR矩陣B = 1 2 3 45 6 7 8 9 1 4 5

2020-05-27 06:43:47

我們?nèi)绾问褂?b class="flag-6" style="color: red">Virtex-4 FPGA的Block-RAM來存儲(chǔ)矩陣/ Vector的內(nèi)容����。例如���,如何在BRAM中存儲(chǔ)矢量A = [1 2 4 5 6 7 9 3]?OR矩陣B = 1 2 3 45 6 7 8 9 1 4 5

2020-05-29 09:16:36

我們?nèi)绾问褂?b class="flag-6" style="color: red">Virtex-4 FPGA的Block-RAM來存儲(chǔ)矩陣/ Vector的內(nèi)容��。例如�����,如何在BRAM中存儲(chǔ)矢量A = [1 2 4 5 6 7 9 3]���?OR矩陣B = [1 2 3 45 6 7 8 9 1 4 5 232 1]

2020-05-29 14:41:56

我是VHDL和FPGA的新手��。我有Virtex-4板����,125 MHz時(shí)鐘�����。我需要為模數(shù)轉(zhuǎn)換(ADC)模塊生成31.25 MHz(分頻125 MHz×4)的串行時(shí)鐘(SCLK)���。任何人都可以幫助

2020-05-25 08:53:55

我有一臺(tái)Memec Virtex-4 FX12 LC開發(fā)板�,并希望使用u***對(duì)電路板進(jìn)行編程�。是否可以使用Platform Cable USB II編程器對(duì)電路板進(jìn)行編程���?謝謝��,雨果

2019-09-27 07:28:35

嗨����,大家好����,首先,如果這篇文章沒有放在正確的主板上��,我想道歉��,我只是不知道在哪里發(fā)布它�����。我使用Xilinx ISE 11.1作為設(shè)計(jì)工具��,現(xiàn)在我想在Virtex 6 FPGA(lx130t)上進(jìn)

2019-02-20 06:42:06

嗨,我即將使用Virtex-4QV設(shè)備(XQR4VFX140)開始一個(gè)新項(xiàng)目�。雖然我對(duì)使用DDR2 / DDR3 SDRAM的Xilinx MIG有一些經(jīng)驗(yàn),但我發(fā)現(xiàn)MIG IP不支持VIRTEX-4QV器件�����。那可能是另類���?如何將DDR2 SDRAM與此FPGA連接����?彌敦道

2020-04-02 06:08:46

近年來���,隨著FPGA技術(shù)的發(fā)展���,支持重構(gòu)的FPGA器件新品迭現(xiàn)。Xilinx��、Altera����、Lattice的FPGA器件都是SRAM查找表結(jié)構(gòu)。Xilinx支持模塊化動(dòng)態(tài)部分重構(gòu)的器件族有

2011-05-27 10:23:28

先生: 我在virtex-4 SX35上使用浮點(diǎn)運(yùn)算符v4.0來實(shí)現(xiàn)浮動(dòng)分頻器��。數(shù)據(jù)表是DS335(2008)�。chipcope圖片在附件中。 A和B上的操作數(shù)是有效的�����,既不溢出����,也不是下溢或下溢

2020-06-12 10:37:08

大家好我想使用Xilinx的Virtex-4芯片學(xué)習(xí)VHDL FPGA編程,以便:1.真正學(xué)習(xí)貿(mào)易(我是初學(xué)者�����,想在真實(shí)芯片上進(jìn)行FPGA編程)����。2.開發(fā)我自己的片上系統(tǒng),這將成為實(shí)驗(yàn)設(shè)備的一部分

2018-09-28 16:54:33

你好�����。我是韓國(guó)LCD& Video Enginner使用各種Xilinx FPGA�。我想看看Virtex-4 Video Starter Kit CD。如何收到Virtex-4視頻入門套件

2020-06-12 16:17:40

鎖定信號(hào)的上升沿是否與virtex-4 FPGA中DCM生成時(shí)鐘的上升沿對(duì)齊�?

2020-07-13 09:50:56

/fpga_sys_planner.htmVirtex-5 FXT, Virtex-5 LX, Virtex-5 LXT, Virtex-5 SXT, Virtex-4 FX, Virtex-4 LX, Virtex-4 SX

2013-03-14 11:49:58

適用于Xilinx Virtex-7 FPGA開發(fā)板的32位DDR4 SDRAM

2020-12-30 07:39:14

我在同一JTAG鏈上有一個(gè)帶有8個(gè)器件的電路板:4個(gè)Xilinx XCF32P閃存�,2個(gè)Xilnix Virtex-5 LX155和2個(gè)Broadcom PHY����。4個(gè)Xilinx EPROMS和2個(gè)

2020-06-03 12:38:25

你好在使用Platform cable USB(使用XilinxISE7.1i)配置virtex-4(sx35)時(shí),我會(huì)關(guān)閉并打開以下消息��。錯(cuò)誤iMPACT 583-'1':從設(shè)備讀取的idcode

2020-06-15 09:27:55

品牌XILINX封裝BGA批次新批次數(shù)量1250制造商Xilinx Inc.系列Virtex?-4 LX電壓 - 供電1.14V ~ 1.26V安裝類型表面貼裝型工作溫度-40°C ~ 100°C

2022-04-19 09:49:09

賽靈思多平臺(tái)Virtex-4 FPGA的性能及應(yīng)用

賽靈思(Xilinx)的Virtex-4現(xiàn)場(chǎng)可編程門陣列(FPGA)是首款基于ASMBL(Advanced Silicon Modular Block)架構(gòu)的多平臺(tái)FPGA系列����。通過采用不同的平臺(tái)(LX、FX

2009-06-26 08:11:39 41

41 Xilinx公司的Virtex-5 FXT FPGA器件在業(yè)界率先集成了嵌入式PowerPC 440處理器模塊�����、高速RocketIO GTX收發(fā)器和專用XtremeDSP 處理能力。作為65nm Virtex-5系列的第四款平臺(tái)�,Virtex-5 FXT提供了極高的

2009-11-24 11:17:22 32

32 FPGA, PowerPC, Virtex-4, 開發(fā)平臺(tái),嵌入式系統(tǒng),通信,數(shù)字視頻, 微處理器摘要:Xilinx公司的Virtex-4 ML403嵌入開發(fā)平臺(tái)是入門級(jí)的開發(fā)環(huán)境,它采用Xilinx的器件XC4VFX12-FF668-10C,支持多個(gè)時(shí)鐘源

2009-11-24 11:33:00 85

85 Virtex-5FPGA系列器件自帶的系統(tǒng)監(jiān)測(cè)器模塊為數(shù)字多普勒接收機(jī)中片上溫度和供應(yīng)電壓的監(jiān)測(cè)提供一種簡(jiǎn)單而高效的解決方案。在Xilinx ISE10.1開發(fā)平臺(tái)中���,利用Xilinx提供的系統(tǒng)監(jiān)測(cè)器模

2010-02-11 11:09:59 24

24 Virtex-4 FPGA應(yīng)用指南

使用Virtex-4器件的DDR2控制器(267MHz及以上)

DDR2SDRAM器件提供了比DDRSDRAM指標(biāo)所要求的更好的新功能��,并允許DDR2器件以666Mb/s的數(shù)據(jù)

2010-05-13 14:14:26 39

39 Virtex-4 系列應(yīng)用指南

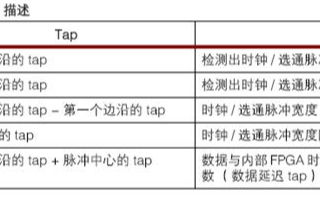

利用直接時(shí)鐘控制技術(shù)實(shí)現(xiàn)存儲(chǔ)器接口數(shù)據(jù)采集

本應(yīng)用指南介紹了在 VirtexTM-4 器件中實(shí)現(xiàn)存儲(chǔ)器接口的直接時(shí)鐘控制數(shù)據(jù)采集

2010-05-13 14:16:59 22

22 賽靈思推出最新Virtex-6/Spartan-6 FPGA 連接開發(fā)套件

近日���,賽靈思公司(Xilinx, Inc. )宣布推出最新Virtex-6 和 Spartan-6 FPGA連接開發(fā)套件,該套件將為客戶提供一個(gè)綜合的��、易用的

2009-12-15 08:42:01 978

978 安富利推出Xilinx Virtex-6 FPGA DSP開發(fā)工具套件安富利公司旗下運(yùn)營(yíng)機(jī)構(gòu)安富利電子元件宣布推出Xilinx Virtex -6 FPGA DSP開發(fā)工具套件����。這套件是為DSP設(shè)計(jì)而打造,是Xilinx目標(biāo)設(shè)計(jì)平

2010-04-24 09:56:31 1331

1331 基于電源模塊���、外部存儲(chǔ)器和FPGA 器件等具體分析了融合系統(tǒng)的低功耗設(shè)計(jì)��。FPGA 器件選擇了Xilinx 公司針對(duì)高性能信號(hào)處理的Virtex24 SX35 三百萬門級(jí)芯片,電源模塊采用TI 公司的兩片TPS5

2011-05-14 11:09:24 34

34 Xilinx Virtex-4 LX160/200 開發(fā)工具套件提供了讓設(shè)計(jì)師加速產(chǎn)品上市的完整硬件環(huán)境���。本套件針對(duì) Xilinx 創(chuàng)新的 Virtex-4 Platform FPGA 系列���,為設(shè)計(jì)的開發(fā)和測(cè)試提供了穩(wěn)定的平臺(tái)。

2012-01-17 14:08:38 2293

2293

Xilinx 的 Virtex-4 系列將高級(jí)硅片組合模塊 (ASMBL) 架構(gòu)與種類繁多的靈活功能相結(jié)合��,大大提高了可編程邏輯設(shè)計(jì)能力����,從而成為替代 ASIC 技術(shù)的強(qiáng)有力產(chǎn)品�����。Virtex-4 FPGA 由 LX��、FX 和 SX 三

2012-01-17 16:14:24 6

6 The PPC405 Virtex-4 is a wrapper around the Virtex-4PowerPC 405 Processor Block primitive.

2012-02-10 16:57:58 38

38 本文是關(guān)于 xilinx公司的7系列FPGA應(yīng)用指南��。xilinx公司的7系列FPGA包括3個(gè)子系列���,Artix-7���、 Kintex-7和Virtex-7。本資料就是對(duì)這3各系列芯片的介紹���。 下表是xilinx公司的7系列FPGA芯片容量對(duì)比表

2012-08-07 17:22:55 201

201 DB46 Xilinx Virtex4-XC4VSX35 電路板設(shè)計(jì)��,注意:用AD10繪制的圖��,低于AD10的版本無法打開��。

2016-01-11 11:28:22 0

0 DB46 Xilinx Virtex4-XC4VSX35 電路板設(shè)計(jì)

2016-02-17 11:52:52 0

0 Xilinx Virtex4-XC4VSX35

2016-02-17 15:08:08 0

0 Memec Virtex4 LX25 LC - TSK3000

2016-02-22 15:56:32 0

0 除了豐富的時(shí)鐘網(wǎng)絡(luò)以外����,Xilinx還提供了強(qiáng)大的時(shí)鐘管理功能,提供更多更靈活的時(shí)鐘�。Xilinx在時(shí)鐘管理上不斷改進(jìn),從Virtex-4的純數(shù)字管理單元DCM�����,發(fā)展到Virtex-5CMT(包含

2017-02-11 09:14:01 1030

1030

PMP9475 12V 輸入?yún)⒖荚O(shè)計(jì)以緊湊高效的設(shè)計(jì)提供為 Xilinx's Virtex? Ultrascale? 系列 FPGA 供電時(shí)所需的所有電源軌���。此設(shè)計(jì)使用幾個(gè) TI 的 PMBus 負(fù)載點(diǎn)電壓穩(wěn)壓器以簡(jiǎn)化臨界軌的設(shè)計(jì)/配置和遙測(cè)����。

2017-02-16 17:50:12 1301

1301

樹結(jié)構(gòu) 針對(duì)不同類型的器件��,Xilinx公司提供的全局時(shí)鐘網(wǎng)絡(luò)在數(shù)量����、性能等方面略有區(qū)別����,下面以Virtex-4系列芯片為例�,簡(jiǎn)單介紹FPGA全局時(shí)鐘網(wǎng)絡(luò)結(jié)構(gòu)。

2017-11-22 07:09:36 8891

8891

All Programmable 技術(shù)和器件的全球領(lǐng)先企業(yè)賽靈思公司(Xilinx�, Inc. (NASDAQ:XLNX))日前宣布NEC公司的iPASOLINK毫米波通信系統(tǒng)將采用其Virtex?-7 FPGA器件。

2018-05-08 15:28:00 1022

1022 該應(yīng)用報(bào)告為工程師設(shè)計(jì)Xilinx 2.5-V和1.8V VirTEX多電壓FPGA產(chǎn)品提供參考��。它提供了關(guān)于工程師沒有遇到多電壓型產(chǎn)品所面臨的問題的基本信息��。

2018-05-23 09:48:46 7

7 ICHEC討論了FPGA對(duì)HPC應(yīng)用的適用性��,并重點(diǎn)介紹了能夠利用特定FPGA上所有DSP的器件的最佳數(shù)據(jù)模式�����。

利用Xilinx Virtex-7 FPGA和Kintex KU115��,ICHEC充分利用了re

2018-11-20 06:42:00 2425

2425 在本視頻中����,了解Xilinx采用高帶寬存儲(chǔ)器(HBM)和CCIX技術(shù)的16nm Virtex UltraScale + FPGA的功能和存儲(chǔ)器帶寬���。

2018-11-27 06:20:00 3624

3624 關(guān)鍵詞:Avnet , FPGA , LX75T , Spartan-6 , Xilinx Avnet公司的Xilinx Spartan-6 FPGA LX75T FPGA開發(fā)板采用Xilinx公司

2019-02-18 16:03:01 920

920 本文檔的主要內(nèi)容詳細(xì)介紹的是VIRTEX-6 FPGA-1L速度等級(jí)LX75T���、LX130T����、LX195T��、LX240T��、LX365T����、LX550T、LX760��、SX315T和SX475T生產(chǎn)勘誤表���。

2019-02-18 16:02:40 1

1 本文檔的主要內(nèi)容詳細(xì)介紹的是virtex-6 FPGA LX760����、LX550T���、LX365T��、LX240T����、LX195T、LX130T�、SX475T和SX315T CES勘誤表。

2019-02-19 10:47:14 5

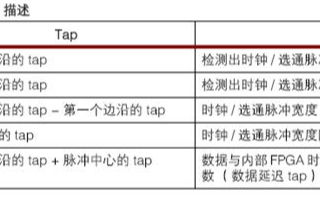

5 大多數(shù)存儲(chǔ)器接口都是源同步接口���,從外部存儲(chǔ)器器件傳出的數(shù)據(jù)和時(shí)鐘/ 選通脈沖是邊沿對(duì)齊的��。在 Virtex-4 器件采集這一數(shù)據(jù)��,需要延遲時(shí)鐘/ 選通脈沖或數(shù)據(jù)�����。利用直接時(shí)鐘控制技術(shù),數(shù)據(jù)經(jīng)延遲

2020-11-26 10:01:31 1219

1219

Virtex-4�、Virtex-5和Spartan-3系列器件增加和修改了一些與配置有關(guān)的專用引腳,這些專用引腳如下���。

2021-01-06 17:13:52 14

14 本節(jié)介紹0.80 mm和1.00 mm間距倒裝芯片細(xì)間距BGA封裝中Virtex-4設(shè)備的引腳����。Virtex-4設(shè)備僅在高性能倒裝芯片BGA封裝中提供��,這些封裝經(jīng)過優(yōu)化設(shè)計(jì),可改善信號(hào)完整性和抖動(dòng)

2021-01-25 08:00:00 4

4 本應(yīng)用指南描述了在 Virtex?-4 XC4VLX25 FF668 -10C 器件中實(shí)現(xiàn)的 DDR SDRAM 控制器�����。該實(shí)現(xiàn)運(yùn)用了直接時(shí)鐘控制技術(shù)來實(shí)現(xiàn)數(shù)據(jù)采集�����,并采用自動(dòng)校準(zhǔn)電路來調(diào)整數(shù)據(jù)線上的延遲���。

2021-03-26 14:42:41 4

4

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論