電平觸發(fā)與尖峰脈沖的模塊功能介紹

電平觸發(fā)是在高或低電平保持的時(shí)間內(nèi)觸發(fā),而邊沿觸發(fā)是由高到低或由低到高這一瞬間觸發(fā)在數(shù)字電平變化的電....

RAM的項(xiàng)目設(shè)計(jì)需求與操作步驟

RAM也叫主存,是與CPU直接交換數(shù)據(jù)的內(nèi)部存儲(chǔ)器。它可以隨時(shí)讀寫(刷新時(shí)除外),而且速度很快,通常....

FIFO項(xiàng)目設(shè)計(jì)需求與操作步驟

在計(jì)算機(jī)中,先入先出隊(duì)列是一種傳統(tǒng)的按序執(zhí)行方法,先進(jìn)入的指令先完成并引退,跟著才執(zhí)行第二條指令(指....

層次化設(shè)計(jì)方法講解

層次化設(shè)計(jì)是指在一個(gè)大型設(shè)計(jì)任務(wù)中,將目標(biāo)層分解,在各個(gè)層次上進(jìn)行設(shè)計(jì)的方法。

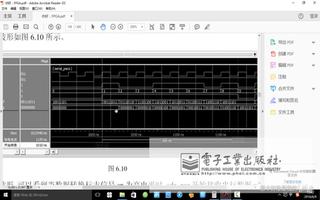

位拼運(yùn)算符的代碼實(shí)例與仿真波形講解

位拼運(yùn)算符是將多個(gè)小的表達(dá)式合并形成一個(gè)大的表達(dá)式,用符號(hào){}來實(shí)現(xiàn)多個(gè)表達(dá)式的連接運(yùn)算,各個(gè)表達(dá)式....

縮減運(yùn)算符的工程實(shí)例講解

縮減運(yùn)算符是單目運(yùn)算符,也有與或非運(yùn)算。其與或非運(yùn)算規(guī)則類似于位運(yùn)算符的與或非運(yùn)算規(guī)則,但其運(yùn)算....

串并轉(zhuǎn)換的需求分析與頂層框架設(shè)計(jì)

串并轉(zhuǎn)換是完成串行傳輸和并行傳輸這兩種傳輸方式之間轉(zhuǎn)換的技術(shù)。移位寄存器可以實(shí)現(xiàn)并行和串行輸入和輸出....

移位運(yùn)算符的應(yīng)用實(shí)例講解

移位運(yùn)算符在程序設(shè)計(jì)中,是位操作運(yùn)算符的一種。移位運(yùn)算符可以在二進(jìn)制的基礎(chǔ)上對(duì)數(shù)字進(jìn)行平移。按照平移....

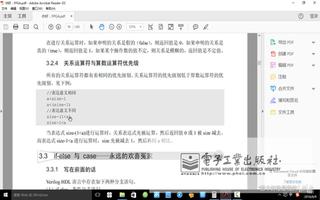

關(guān)系運(yùn)算符的種類與使用意義

“運(yùn)算符用于執(zhí)行程序代碼運(yùn)算,會(huì)針對(duì)一個(gè)以上操作數(shù)項(xiàng)目來進(jìn)行運(yùn)算。例如:2+3,其操作數(shù)是2和3,而....

設(shè)計(jì)ROM項(xiàng)目的需求與操作步驟

ROM是只讀存儲(chǔ)器(Read-Only Memory)的簡(jiǎn)稱,是一種只能讀出事先所存數(shù)據(jù)的固態(tài)半導(dǎo)體....

FPGA之FIFO練習(xí)2:設(shè)計(jì)思路

FIFO( First Input First Output)簡(jiǎn)單說就是指先進(jìn)先出。由于微電子技術(shù)的....

FPGA之簡(jiǎn)單代碼的重要性

不管是學(xué)FPGA還是C語言,任何一種代碼的學(xué)習(xí)都離不開大量的代碼閱讀,也就是多看,多學(xué)習(xí)別人的代碼。....

FPGA之異步練習(xí):設(shè)計(jì)思路

在異步設(shè)計(jì)中,完全避免亞穩(wěn)態(tài)是不可能的。因此,設(shè)計(jì)的基本思路應(yīng)該是:首先盡可能減少出現(xiàn)亞穩(wěn)態(tài)的可能性....

FPGA之異步練習(xí)1:設(shè)計(jì)思路

基于FPGA的數(shù)字系統(tǒng)設(shè)計(jì)中大都推薦采用同步時(shí)序的設(shè)計(jì),也就是單時(shí)鐘系統(tǒng)。但是實(shí)際的工程中,純粹單時(shí)....

FPGA之流水線練習(xí)3:設(shè)計(jì)思路

流水線主要是一種硬件設(shè)計(jì)的算法,如第一條中表述的流水線設(shè)計(jì)就是將組合邏輯系統(tǒng)地分割,并在各個(gè)部分(分....

如何驗(yàn)證IP核的代碼

流水線縮短了在一個(gè)時(shí)鐘周期內(nèi)給的那個(gè)信號(hào)必須通過的通路長度,增加了數(shù)據(jù)吞吐量,從而可以提高時(shí)鐘頻率,....

FPGA之流水線練習(xí)1:設(shè)計(jì)思路

流水線設(shè)計(jì)就是將組合邏輯系統(tǒng)地分割,并在各個(gè)部分(分級(jí))之間插入寄存器,并暫存中間數(shù)據(jù)的方法。目的是....

FPGA之流水線練習(xí)4:設(shè)計(jì)思路

流水線設(shè)計(jì)就是將組合邏輯系統(tǒng)地分割,并在各個(gè)部分(分級(jí))之間插入寄存器,并暫存中間數(shù)據(jù)的方法。目的是....

至芯科技:FPGA教學(xué)視頻(1)

至芯科技成立于2010年,是一家致力于高新技術(shù)培訓(xùn)和移動(dòng)互聯(lián)網(wǎng)知識(shí)傳播的教育及研發(fā)機(jī)構(gòu)。時(shí)刻更新,精....

MAX II的UFM模塊使用實(shí)例

UFM產(chǎn)品是一種在線部署于局域網(wǎng)與廣域網(wǎng)之間的All-in-One式的多功能高性能流量監(jiān)測(cè)、控制、管....

265色VGA顯示實(shí)驗(yàn)

VGA接口共有15針,分成3排,每排5個(gè)孔,顯卡上應(yīng)用最為廣泛的接口類型,絕大多數(shù)顯卡都帶有此種接口....

時(shí)序基礎(chǔ)分析

時(shí)序分析是以分析時(shí)間序列的發(fā)展過程、方向和趨勢(shì),預(yù)測(cè)將來時(shí)域可能達(dá)到的目標(biāo)的方法。此方法運(yùn)用概率統(tǒng)計(jì)....