IP設計中的注意事項

以下是一些在IP設計過程中可以使用的策略。雖然IP設計和驗證是一個非常耗時的階段,但如果設計需要新的....

使用Modelsim編譯激勵文件的詳細流程

對于激勵文件,我常用的是直接手寫,最初學這個的時候,好像是用的Quartus里的那個Modelsim....

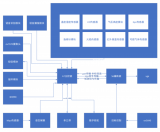

卷積神經(jīng)網(wǎng)絡介紹 基于LeNet5實現(xiàn)的手寫字符識別

前文中,我們介紹了一些傳統(tǒng)計算機視覺的算法,包括降噪濾波、二值化、縮放、銳化等,最終我們在FPGA上....

常用銳化算法及Sobel銳化的介紹

物體的邊緣是以圖像局部特性不連續(xù)性的形式出現(xiàn)的,即邊緣意味著一個區(qū)域的結(jié)束和另一個區(qū)域的開始。圖像邊....

如何尋找時序路徑的起點與終點

左邊的電路圖是需要分析的電路,我們的目的是要對此電路進行時序分析,那首先要找到該電路需要分析的時序路....

歐姆定律加基爾霍夫電流定律等于更好的人工智能

對大多數(shù)計算機來說,在外部存儲器和計算資源(如CPU和GPU)之間移動大量數(shù)據(jù)耗費的時間成本和能源成....

JESD204B標準的ADC與FPGA的接口

與現(xiàn)有接口格式和協(xié)議相比,JESD204B接口更復雜、更微妙,必須克服一些困難才能實現(xiàn)其優(yōu)勢。像其他....

基于英特爾FPGA的全新解決方案

基于服務器的集中式架構(gòu)常常無法提供冗余故障點,從而推高成本和加重維護負擔。同時,大型服務器往往會占據(jù)....

?FPGA便捷開發(fā)-TCL商店(開源)

傳統(tǒng)的FPGA開發(fā)都是通過GUI界面進行相關(guān)的“按鈕”式操作,Vivado則在引入Tcl解釋器后,可....

FPGA中HP/HR/HD Bank的應用

在開發(fā)FPGA綁定管腳時,經(jīng)常會看到HP Bank、HR Bank和HD Bank,它們分別是什么意....

Xilinx FFT IP介紹與仿真測試

Xilinx快速傅立葉變換(FFT IP)內(nèi)核實現(xiàn)了Cooley-Tukey FFT算法,這是一種計....

Wi-Fi標準簡介:Wi-Fi 6和Wi-Fi 7

Wi-Fi 6 是 IEEE 802.11ax 的公開名稱。Wi-Fi 6 于 2021 年初獲得全....

如何在工程的XDC文件里加入GT位置約束

等該例子工程跑完綜合,實現(xiàn),并產(chǎn)生bit文件之后,請將PDI文件加載到你的VPK120里面:

關(guān)于指數(shù)對比度增強FPGA實現(xiàn)

對比度增強是個廣泛的話題,前文中關(guān)于直方圖均衡的方法,其實就是一種對比度增強。而對比度增強,就是提高....

基于軟件的Vitis AI 2.0加速解決方案

Vitis AI 2.0 全面發(fā)布!作為賽靈思 FPGA 和自適應 SoC 上最綜合全面的基于軟件的....

FPGA工程師如何提升自己的算法能力

作為一名FPGA工程師,我們的任務就是把某些特定的邏輯行為雕刻到FPGA芯片上,通過設計邏輯電路達到....

Vivado與ModelSim的聯(lián)合仿真操作

Vivado自帶的仿真,個人覺得跑一些小模塊的仿真還是可以的,不過跑大的仿真系統(tǒng),容易無體驗感,建議....

以工程的形式來介紹ModelSim的仿真使用

本篇將以工程的形式來介紹ModelSim的仿真使用,工程一般由:根目錄+源碼+work庫+資源庫+仿....

基于FPGA的高速高精度聲源定位系統(tǒng)技術(shù)特點

第一部分 設計概述 / Design Introduction 1.1 設計目的 頻繁雜亂的鳴笛聲,....

探究FPGA的圖像及視頻加密解密系統(tǒng)

第一部分 設計概述 1.1 設計目的 在多媒體技術(shù)高度發(fā)展的今天,視頻信息安全愈發(fā)受到人們的關(guān)注。傳....

自動ECO參考網(wǎng)表來自動修改實現(xiàn)網(wǎng)表

本次發(fā)布帶來了如下幾個重要的更新: 新增RTL Patch ECO,無需重新綜合,節(jié)省了大量時間 直....

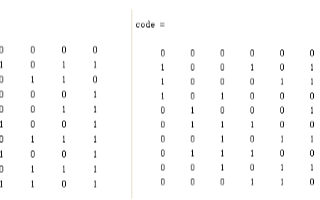

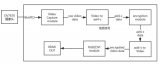

基于FPGA實現(xiàn)擴頻通信模塊的設計方案與仿真

在無線通信系統(tǒng)中,普遍使用擴頻通信技術(shù),因此擴頻技術(shù)對通信系統(tǒng)具有重要的現(xiàn)實意義。直接序列擴頻技術(shù)是....