Introduction

There are many types of cables or physical data-transmission media available to transfer high-speed serial data from one device to another. The type of cable chosen for a serial link depends principally on the application, characteristics of the cable, and cost considerations. The shielded twisted pair (STP) cable has been the most commonly used cable for many serializer/deserializer (SerDes) applications because of its improved signal-to-noise ratio, crosstalk, and ability to transfer balanced differential signals with the best quality.The MAX9259/MAX9260 SerDes chipset has two accompanying evaluation (EV) kits and characterization boards, the MAX9259EVKIT and MAX9260EVKIT. These EV kits were initially designed with Rosenberger interconnects and utilizing an STP cable as a transmission media to achieve the highest speed at maximum distance. The MAX9259/MAX9260 chipset has been tested and verified to perform well and meet the device specification with a STP cable. However, this type of cable may not be the only and most cost effective solution for the gigabits multimedia serial link (GMSL) technology.

This application note presents data showing that the device settings can be optimized to work equally well with coax cables at various lengths. This flexibility with coax cables will be especially beneficial for GMSL technology.

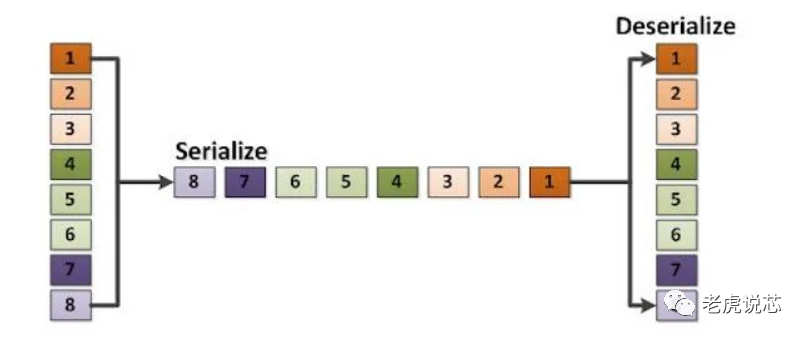

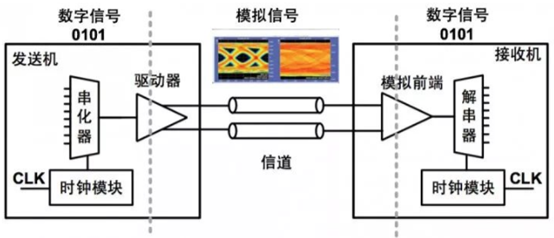

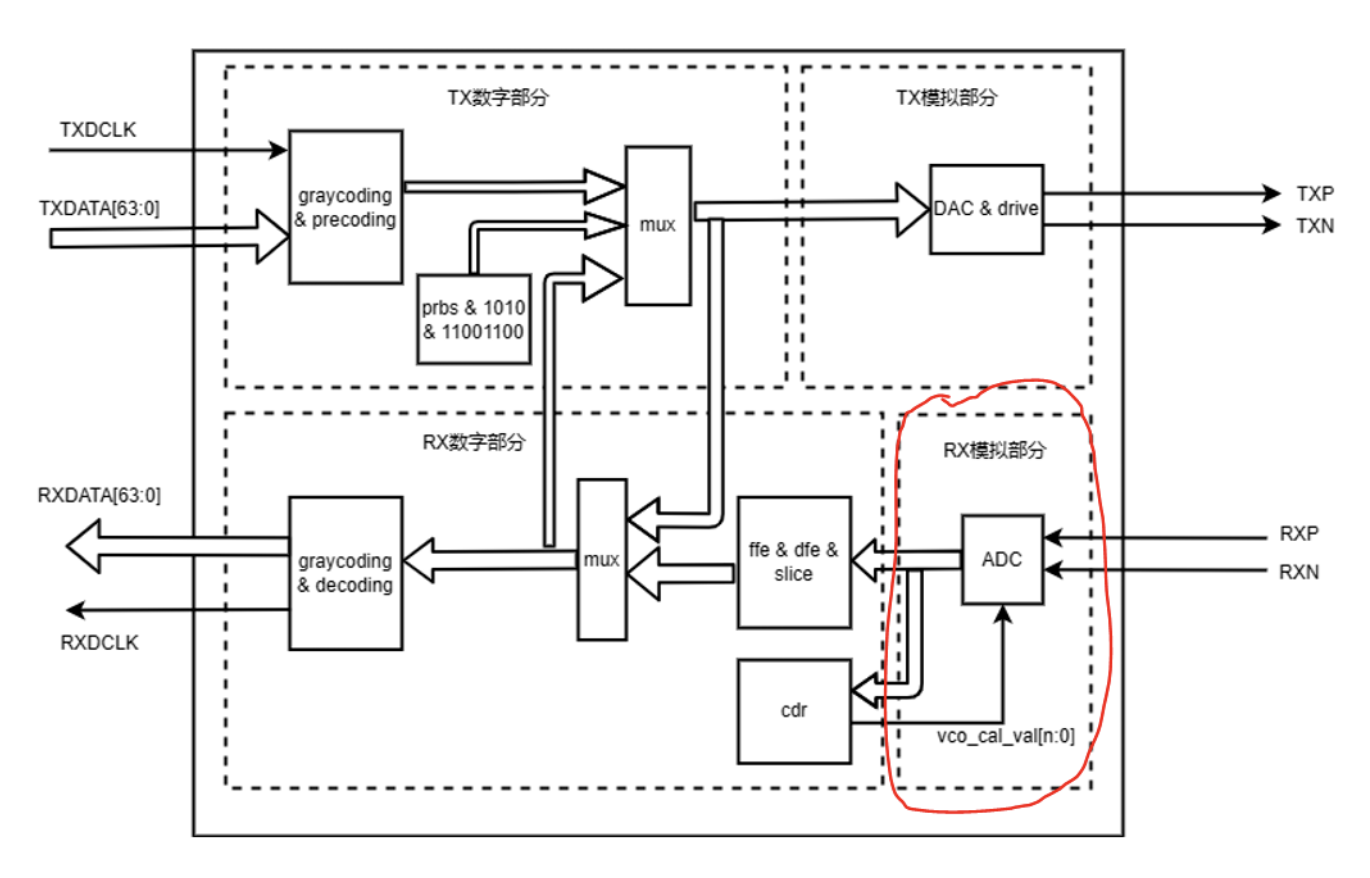

Basic operation of the SerDes chipset

In the MAX9259/MAX9260 SerDes chipset, transmitter preemphasis and receiver equalization settings are available to compensate for losses across the transmission medium. These capabilities allow the designer to experiment and determine whether the same performance can be achieved with inexpensive cables and connectors.

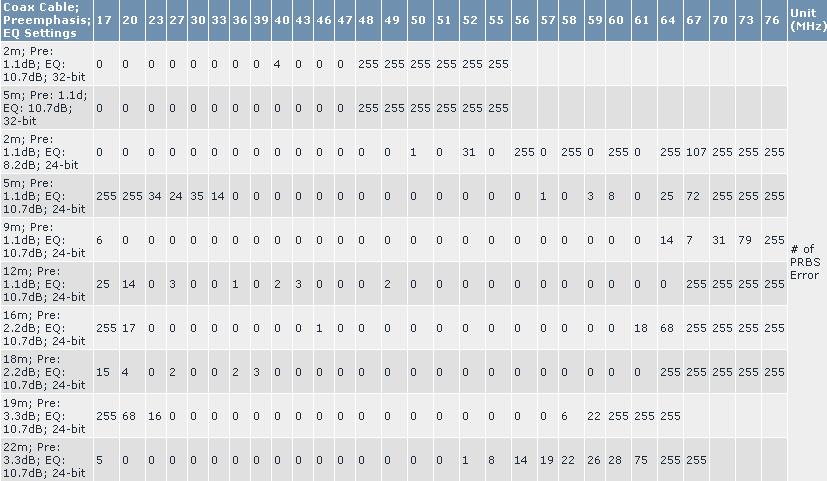

Table 1 summarizes the MAX9259/MAX9260 chipset's pseudo-random bit sequence (PRBS) test performed with the preemphasis and equalizer settings optimized for a specific coax cable length. In both configurations, 24-bit (16.66MHz to 104MHz) and 32-bit (12.5MHz to 78MHz) mode, there are fewer bit errors at low-frequency settings, but increasingly more bit errors as the pixel clock-frequency range limits are reached.

Table 1. PRBS Results for the MAX9259/MAX9260 characterization board; testing done with different coax cable lengths*

*Data generated on MAX9259/MAX9260 characterization boards with PRBS testing and preemphasis enabled; with optimal EQ settings for various coax cables across PCLK frequencies; and at room temperature and with a nominal supply voltage.

This application note describes the setup and conditions for these tests. It also details the correct register settings for the on-chip preemphasis and equalizer circuits to optimize the performance (e.g., the eye opening) for different coax cable lengths from 2m to 22m. Note that the setup utilizes both the MAX9259EVKIT and MAX92560EVKIT and their characterization boards (Figure 1) for optimized high-speed performance. In this test the EV kits and software GUI were used to control the serializer settings; the characterization board has been designed to achieve an optimized eye opening even at long cable distances.

Testing the chipset

Device setup conditions

- BWS: 24-bit bus mode (JU2 = 0); 32-bit bus mode (JU2 = 1)

- DRS: 24-bit 16.7MHz to 104MHz (JU4 = 0); 32-bit 12.5MHz to 78MHz (JU4-1)

- SSC: Off (JU5 = 0)

- MAX9259: VDDD, VDDA, VDDIO = 1.8V

- MAX9260: VDDA, VDDD, VDDIO = 3.3V

- EQS: 5.2dB (JU9 = 1); 10.7dB (JU9 = 0)

Measurement setup

Figure 1. Test setup for coax cable PRBS tests.

Coax cable connection

The center/core of the coax cable was connected from the MAX9259's OUT+ pin to the MAX9260's IN+ pin on the MAX9259/MAX9260 characterization boards. Both ends of the metallic shield of the coax cable were connected to ground on the board. The MAX9259's OUT- pin, which is closer to the device, was connected to 3.3V.

Optimizing the preemphasis settings procedure

To begin the testing procedure, follow these guidelines to power up the EV kits and start the software.

- Verify that all jumpers are set in their default positions. For default shunt positions, see Table 1 in the manual that came with the MAX9259EVKIT and MAX9260EVKIT.

- Connect a coax cable from the MAX9259EVKIT to the MAX9260EVKIT.

- Verify the MAX9259 EVKIT jumper positions for JU1 (2-3), JU9 (1-2), and JU10 (shunt) before plugging in the USB cable.

- Verify the MAX9260EVKIT jumper positions for JU1 (2-3), JU11 (1-2), and JU10 (open).

- Set the Agilent 33250A Arbitrary Waveform Generator (AWG) parameters to the desired pixel clock frequency (e.g., square wave at 20MHz). Settings are: amplitude, 1.8V; offset, 900mV; duty cycle, 50%.

- Start the MAX9259EVKIT/MAX9260EVKIT program.

- Click the Read All '59 button, and verify that all MAX9259 registers are accessible (Figure 2).

More detailed image (PDF, 1.3MB)

Figure 2. MAX9259EVKIT/MAX9260EVKIT GUI and the MAX9259 tab.

- Next, enable the PRBS mode by checking the PRBSEN box and click the Write button on the right side of Register 0x04.

- Select the different PREEMP settings from the drop-down menu and click the Write button on the right side of the Register 0x05.

- Utilizing the high-bandwidth scope, monitor the eye-diagram width and height at the receiver end of the coax cable.

- Determine the optimal preemphasis settings for the length of coax cable used.

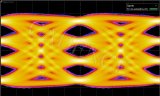

Figure 3, 4, and 5 show the eye-diagram measurements achieved with a high-bandwidth scope used at the receiver to determine the optimal preemphasis settings.

More detailed image (PDF, 3.3MB)

Figure 3. PRBS mode eye diagram (pixel clock at 30MHz, 9m coax cable, preemphasis off).

More detailed image (PDF, 3.4MB)

Figure 4. PRBS mode eye diagram (pixel clock at 30MHz, 9m coax cable, +1.1dB preemphasis).

More detailed image (PDF, 3.2MB)

Figure 5. PRBS mode eye diagram (pixel clock at 30MHz, 9m coax cable, +2.2dB preemphasis).

Optimizing the equalizer settings procedure

To begin the testing procedure, follow these guidelines to power up the EV kits and start the software.

- Apply the optimum preemphasis settings to the MAX9259 for the desired coax cable length.

- Connect the coax cable from the MAX9259EVKIT to the MAX9260EVKIT.

- From the EV kit GUI (Figure 6), switch to the MAX9260 tab and click the Read All '60 button to verify that all MAX9260 registers are accessible.

- Next, enable the PRBS mode by checking the PRBSEN box and click the Write button on the right side of Register 0x04.

- Selected the different EQTUNE settings from the drop-down menu and click the Write button on the right side of the Register 0x05.

More detailed image (PDF, 1.4MB)

Figure 6. MAX9259EVKIT/MAX9260EVKIT GUI, MAX9260 tab.

- Switched to the PRBS Test tab, and set the duration to 5s as shown in Figure 7.

More detailed image (PDF, 1MB)

Figure 7. MAX9259EVKIT/MAX9260EVKIT GUI, PRBS Test tab.

- Click the Start button to run the PRBS test and wait 5s for it to finish.

- Based on the numbers of PRBS bit-errors accumulated over 5 seconds, the optimal receiver equalization settings will be selected for any of the tested coax cable lengths.

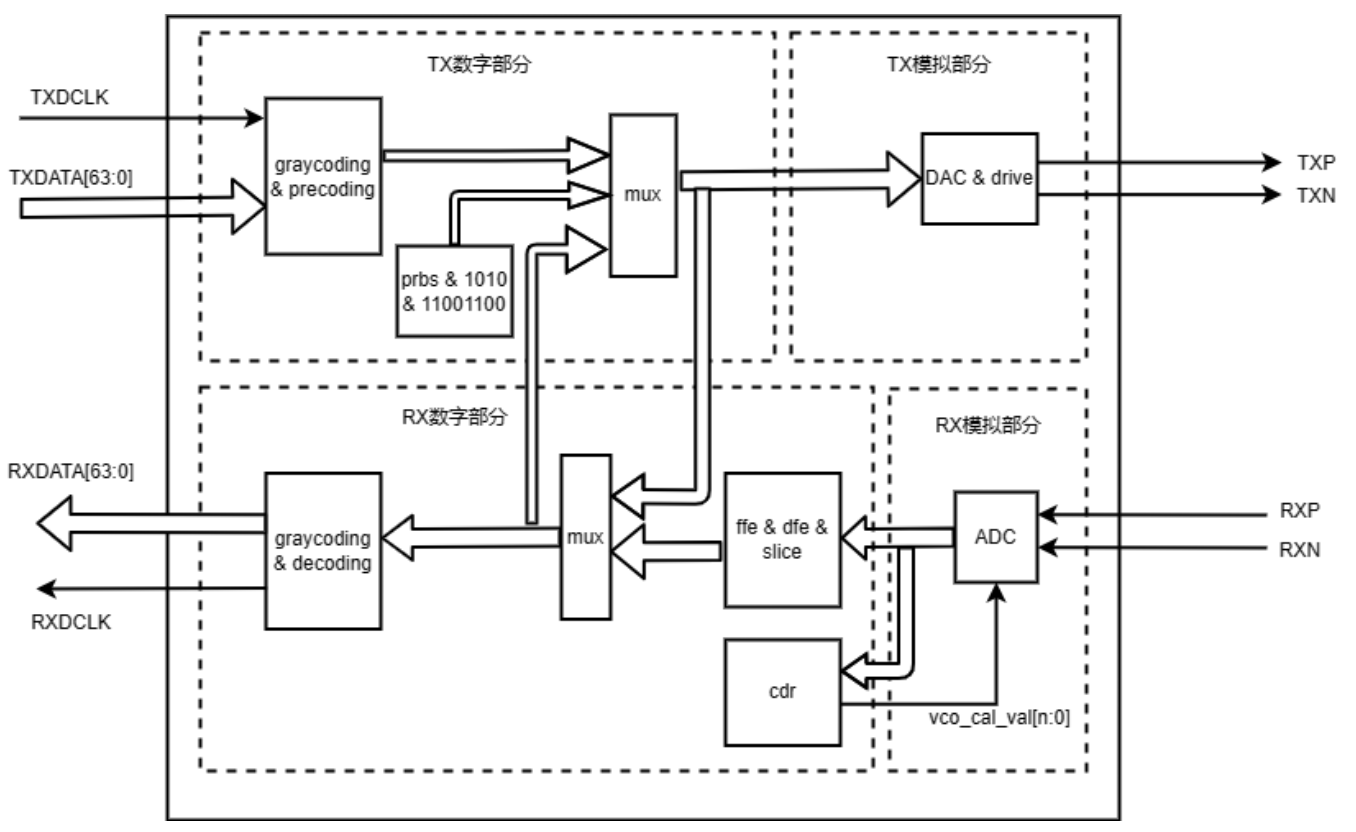

The evaluation results in Table 1 and Figure 8 show that coax cables can indeed be utilized for high-speed serial data transmission supporting the GMSL technology.

Figure 8. PRBS test results with the MAX9259/MAX9260 characterization boards at various coax cables lengths. The PRBS test was for 5s with the preemphasis and EQ settings optimized. Different cable lengths across PCLK. TA = +25°C; used a nominal supply voltage.

電子發(fā)燒友App

電子發(fā)燒友App

評論